# MIC5191

Ultra High-Speed, High-Current Active Filter / LDO Controller

## **General Description**

The MIC5191 is an ultra high-speed linear regulator. It uses an external N-Channel FET as its power device.

The MIC5191's ultra high-speed abilities can handle the fast load demands of microprocessor cores, ASICs, and other high-speed devices. Signal bandwidths of greater than 500 kHz can be achieved with a minimum amount of capacitance while at the same time keeping the output voltage clean, regardless of load demand. A powerful output driver delivers large MOSFETs into their linear regions, achieving ultra-low dropout voltage.

$1.25V_{\text{IN}}$  ±10% can be turned into 1V ±1% without the use of a large amount of capacitance.

MIC5191 (1.0V reference) is optimized for output voltages of 1.0V and higher.

The MIC5191 is offered in 10-pin 3mm×3mm  $MLF^{\mbox{\ensuremath{\mathbb{S}}}}$  and 10-pin MSOP-10 packages and has an operating junction temperature range of  $-40^{\circ}$ C to +125°C.

Data sheets and support documentation can be found on Micrel's web site at www.micrel.com.

### Features

- Input voltage range:  $V_{IN}$  = 1.0V to 5.5V

- +1.0% initial output tolerance

- Dropout down to 25mV@10A

- · Filters out switching frequency noise on input

- Very high large signal bandwidth >500kHz

- PSRR >40dB at 500kHz

- Adjustable output voltage down to 1.0V

- Stable with any output capacitor

- Excellent line and load regulation specifications

- Logic controlled shutdown

- Current limit protection

- 10-pin MLF® and MSOP-10 packages

- Available -40°C to +125°C junction temperature

## Applications

- Distributed power supplies

- ASIC power supplies

- DSP,  $\mu$ P, and  $\mu$ C power supplies

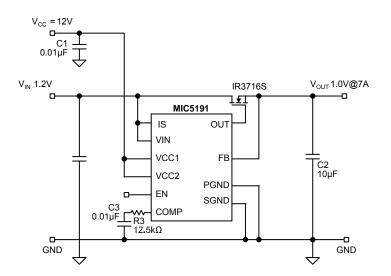

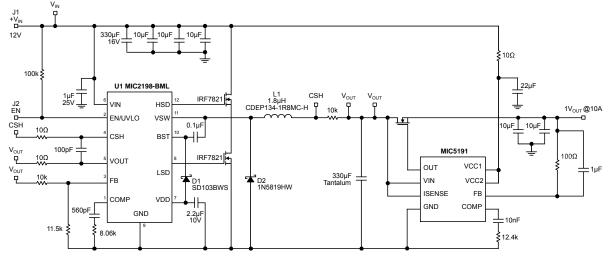

# **Typical Application**

PowerPAK is a trademark of Siliconix, Inc.

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

# **Ordering Information**

| Part Number |            | Voltage | Junction          | Package                           |  |

|-------------|------------|---------|-------------------|-----------------------------------|--|

| Standard    | Pb-Free    | voltage | Temperature Range | Fackage                           |  |

| MIC5191BML  | MIC5191YML | Adj.    | –40° to +125°C    | 10-Pin 3mm x 3mm MLF <sup>®</sup> |  |

| MIC5191BMM  | MIC5191YMM | Adj.    | –40° to +125°C    | 10-Pin MSOP                       |  |

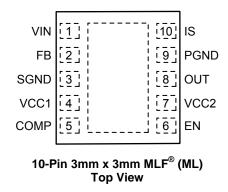

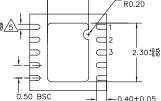

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                     |

|------------|----------|--------------------------------------------------------------------------------------------------|

| 1          | VIN      | Input voltage (current sense +).                                                                 |

| 2          | FB       | Feedback input to error amplifier.                                                               |

| 3          | SGND     | Signal ground.                                                                                   |

| 4          | VCC1     | Supply to the internal voltage regulator.                                                        |

| 5          | COMP     | Error amplifier output for external compensation.                                                |

| 6          | EN       | Enable (Input): CMOS-compatible.<br>Logic high = Enable, Logic low = Shutdown. Do not float pin. |

| 7          | VCC2     | Power to output driver.                                                                          |

| 8          | OUT      | Output drive to gate of power MOSFET.                                                            |

| 9          | PGND     | Power ground                                                                                     |

| 10         | IS       | Current sense.                                                                                   |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN</sub> )                                   | +6.0V                           |

|---------------------------------------------------------------------|---------------------------------|

| Enable Voltage (V <sub>EN</sub> )                                   | +14V                            |

| V <sub>cc</sub> 1, V <sub>cc</sub> 2                                | +14V                            |

| Junction Temperature (T <sub>J</sub> )<br>ESD Rating <sup>(3)</sup> | –40°C ≤ T <sub>J</sub> ≤ +125°C |

| ESD Rating <sup>(3)</sup>                                           |                                 |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>IN</sub> )            | +1.0V to +5.5V                  |

|----------------------------------------------|---------------------------------|

| Enable Voltage (V <sub>EN</sub> )            | 0V to V <sub>CC</sub>           |

| V <sub>CC</sub> 1, V <sub>CC</sub> 2         | +4.5V to +13.2V                 |

| Junction Temperature (T <sub>J</sub> )       | –40°C ≤ T <sub>J</sub> ≤ +125°C |

| Package Thermal Resistance                   |                                 |

| 3x3 MLF-10 (θ <sub>JA</sub> ) <sup>(4)</sup> | 60°C/W                          |

| MSOP-10 (θ <sub>JA</sub> ) <sup>(5)</sup>    | 200°C/W                         |

# Electrical Characteristics<sup>(6)</sup>

$T_A = 25^{\circ}C$  with  $V_{IN} = 1.2V$ ;  $V_{CC} = 12V$ ;  $V_{OUT} = 1.0V$ ; **bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ , unless noted.

| Parameter                                                   | Condition                                   | Min  | Тур   | Max  | Units |

|-------------------------------------------------------------|---------------------------------------------|------|-------|------|-------|

| Output Voltage Accuracy                                     | At 25°C                                     | -1   |       | +1   | %     |

|                                                             | Over temperature range                      | -2   |       | +2   | %     |

| Output Voltage Line Regulation                              | V <sub>IN</sub> = 1.2V to 5.5V              | -0.1 | 0.005 | +0.1 | %/V   |

| Feedback Voltage                                            |                                             | 0.99 | 1     | 1.01 | V     |

| Output Voltage Load Regulation                              | $I_L$ = 10mA to 1A                          |      | 0.02  | 0.5  | %     |

| VCC Pin Current (V <sub>CC</sub> 1 + V <sub>CC</sub> 2)     | Enable = 0V                                 |      | 40    |      | μA    |

| VCC Pin Current (V <sub>CC</sub> sig + V <sub>CC</sub> drv) | Enable = 5V                                 |      | 15    | 20   | mA    |

| VIN Pin Current                                             | Current from V <sub>IN</sub>                |      | 10    | 15   | μA    |

| FB Bias Current                                             |                                             |      | 13    | 30   | μA    |

| Current Limit Threshold                                     |                                             | 35   | 50    | 70   | mV    |

| Start-up Time                                               | $V_{EN} = V_{IN}$                           |      | 25    | 100  | μs    |

| Enable Input Threshold                                      | Regulator enable                            | 0.8  | 0.6   |      | V     |

|                                                             | Regulator shutdown                          |      | 0.5   | 0.2  | V     |

| Enable Hysteresis                                           |                                             |      | 100   |      | mV    |

| Enable Pin Input Current                                    | V <sub>IL</sub> < 0.2V (Regulator shutdown) |      | 100   |      | nA    |

|                                                             | $V_{IH} > 0.8V$ (Regulator enabled)         |      | 100   |      | nA    |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. The device is not guaranteed to function outside its operating rating.

3. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

4. Per JESD 51-5 (1S2P Direct Attach Method).

5. Per JESD 51-3 (1S0P).

6. Specification for packaged product only.

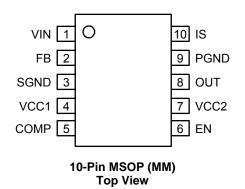

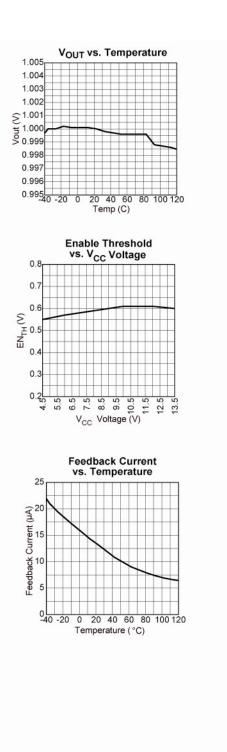

## **Typical Characteristics**

11.5 12.5 13.5

40L

5.5 6.5 7.5

# **Functional Characteristics**

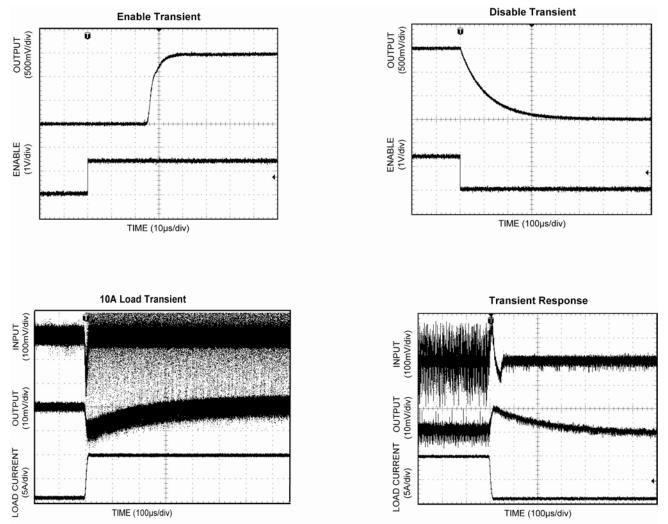

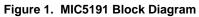

# **Functional Diagram**

# **Functional Description**

#### VIN

The VIN pin is connected to the N-Channel drain. VIN is the input power being supplied to the output. This pin is also used to power the internal current limit comparator and compare the ISENSE voltage for current limit. The voltage range is from 1.0V min to 5.5V max.

#### ISENSE

The ISENSE pin is the other input to the current limit comparator. The output current is limited when the ISENSE pin's voltage is 50mV less than the VIN pin. In cases where there is a current limited source and there isn't a need for current limit, this pin can be tied directly to VIN. Its operating voltage range, like the VIN pin, is 1.0V min to 5.5V max.

### VCC1, VCC2

VCC1 supplies the error amplifier and internal reference, while VCC2 supplies the output gate drive. For this reason, ensure these pins have good input capacitor bypassing for better performance. The operating range is from 4.5V to 13.2V and both VCC pins should be tied together. Ensure that the voltage supplied is greater than a gate-source threshold above the output voltage for the N-Channel MOSFET selected.

#### Output

The output drives the external N-Channel MOSFET and is powered from VCC. The output can sink and source over 150mA of current to drive either an N-Channel MOSFET or an external NPN transistor. The output drive also has short-circuit current protection.

#### Enable

The MIC5191 comes with an active-high enable pin that allows the regulator to be disabled. Forcing the enable pin low disables the regulator and sends it into a low offmode-current state. Forcing the enable pin high enables the output voltage. The enable pin cannot be left floating; a floating enable pin may cause an indeterminate state on the output.

#### FB

The feedback pin is used to sense the output voltage for regulation. The feedback pin is compared to an internal 1.0V reference and the output adjusts the gate voltage accordingly to maintain regulation. Since the feedback biasing current is typically  $13\mu$ A, smaller feedback resistors should be used to minimize output voltage error.

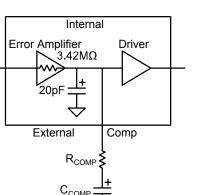

### COMP

COMP is the external compensation pin. This allows complete control over the loop to allow stability for any type of output capacitor, load currents and output voltage. A detailed explanation of how to compensate the MIC5191 is in the *"Designing with the MIC5191"* section.

#### SGND, PGND

SGND is the internal signal ground which provides an isolated ground path from the high current output driver. The signal ground provides the grounding for noise sensitive circuits such as the current limit comparator, error amplifier and the internal reference voltage.

PGND is the power ground and is the grounding path for the output driver.

# Application Information

### Designing with the MIC5191

#### Anatomy of a transient response

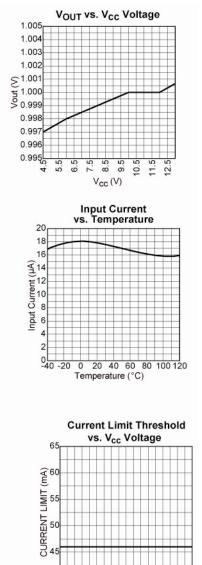

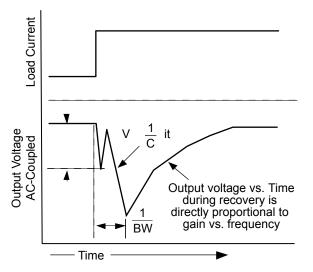

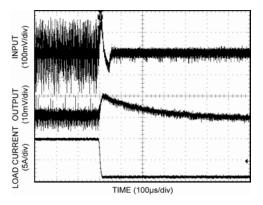

A voltage regulator can maintain a set output voltage while its exterior world is pushing and pulling in its demand for power. The measure of a regulator is generally how accurately and effectively it can maintain that voltage, regardless of how the load demands power. One measure of regulator response is the load step. This is an intuitive look at how the regulator responds to a change in load current. Figure 2 is a look at the transient response to a load step.

Figure 2. Typical Transient Response

At the start of a circuit's power demand, the output voltage is regulated to its set point, while the load current runs at a constant rate. For many different reasons, a load may ask for more current without warning. When this happens, the regulator needs some time to determine the output voltage drop. This is determined by the speed of the control loop. So, until enough time has elapsed, the control loop is oblivious to the voltage change. The output capacitor must bear the burden of maintaining the output voltage.

$$\Delta V = L \frac{di}{dt}$$

Since this is a sudden change in voltage, the capacitor will try to maintain voltage by discharging current to the output. The first voltage drop is due to the output capacitor's ESL (equivalent series inductance). The ESL will resist a sudden change in current from the capacitor and drop the voltage quickly. The amount of voltage drop during this time will be proportional to the output capacitor's ESL and the speed at which the load steps. Slower load current transients will reduce this effect.

$$\Delta V \downarrow = L \frac{di}{dt \uparrow}$$

Placing multiple small capacitors with low ESL in parallel can help reduce the total ESL and reduce voltage droop during high speed transients. For high speed transients, the greatest voltage deviation will generally be caused by output capacitor ESL and parasitic inductance.

$$\Delta V \downarrow = L \downarrow \frac{di}{dt}$$

After the current has overcome the effects of the ESL, the output voltage will begin to drop proportionally to time and inversely proportional to output capacitance.

$$\Delta V = \frac{1}{C} \int i dt$$

The relationship to output voltage variation will depend on two aspects, loop bandwidth and output capacitance. The output capacitance will determine how far the voltage will fall over a given time. With more capacityance, the drop in voltage will fall at a decreased rate. This is the reason that for the same bandwidth, more capacitance provides a better transient response.

$$\Delta V \downarrow = \frac{1}{\uparrow C} \int i dt$$

Also, the time it takes for the regulator to respond is directly proportional to its gain bandwidth. Higher bandwidth control loops respond quicker causing a reduced droop on the supply for the same amount of capacitance.

$$\Delta V \downarrow = \frac{1}{C} \int i dt \downarrow$$

Final recovery back to the regulated voltage is the final phase of transient response and the most important factors are gain and time. Higher gain at higher frequency will get the output voltage closer to its regulation point quicker. The final settling point will be determined by the load regulation, which in proportional to DC (0Hz) gain and the associated loss terms.

There are other factors that contribute to large signal transient response, such as source impedance, phase margin and PSRR. For example, if the input voltage drops due to source impedance during a load transient, this will contribute to the output voltage deviation by filtering through to the output reduced by the loops PSRR at the frequency of the voltage transient. It is straightforward: good input capacitance reduces the source impedance at high frequencies. Having between 35° and 45° of phase margin will help speed up the recovery time. This is caused by the initial overshoot in response to the loop sensing a low voltage.

The MIC5191 allows the flexibility of externally controlling the gain and bandwidth. This allows the MIC5191 design to be tailored to each individual design.

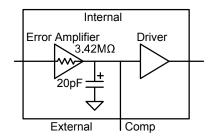

In designing the MIC5191, it is important to maintain adequate phase margin. This is generally achieved by having the gain cross the 0dB point with a single pole 20dB/decad roll-off. The compensation pin is configured as Figure 3 demonstrates.

Figure 3. Internal Compensation

This places a pole at 2.3 kHz at 80dB and calculates as follows.

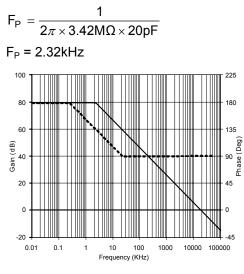

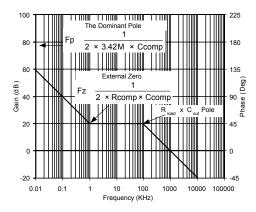

There is single pole roll off. For most applications, an output capacitor is required. The output capacitor and load resistance create another pole. This causes a two-pole system and can potentially cause design instability with inadequate phase margin. What should we do? *Answer*. we compensate it externally. By providing a dominant pole and zero–allowing the output capacitor and load to provide the final pole–a net single pole roll off is created, with the zero canceling the dominant pole. Figure 5 demonstrates:

Figure 5. External Compensation

Placing an external capacitor ( $C_{COMP}$ ) and resistor ( $R_{COMP}$ ) for the external pole-zero combination. Where the dominant pole can be calculated as follows:

$$\mathsf{F}_{\mathsf{P}} = \frac{1}{2\pi \times 3.42 \mathsf{M}\Omega \times \mathsf{C}_{\mathsf{COMP}}}$$

And the zero can be calculated as follows:

$$\mathsf{F}_{\mathsf{Z}} = \frac{1}{2\pi \times \mathsf{R}_{\mathsf{COMP}} \times \mathsf{C}_{\mathsf{COMP}}}$$

This allows for high DC gain, and high bandwidth with the output capacitor and the load providing the final pole.

Figure 6. External Compensation Frequency Response

It is recommended that the gain bandwidth should be designed to be less than 1 MHz. This is because most capacitors lose capacitance at high frequency and becoming resistive or inductive. This can be difficult to compensate for and can create high frequency ringing or worse, oscillations.

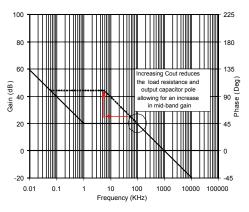

By increasing the amount of output capacitance, transient response can be improved in multiple ways. First, the rate of voltage drop vs. time is decreased. Also, by increasing the output capacitor, the pole formed by the load and the output capacitor decreases in frequency. This allows for the increasing of the compensation resistor, creating a higher mid-band gain.

Figure 7. Increasing Output Capacitance

This will have the effect of both decreasing the voltage drop as well as returning closer and faster to the regulated voltage during the recovery time.

#### **MOSFET Selection**

The typical pass element for the MIC5191 is an N-Channel MOSFET. There are multiple considerations when choosing a MOSFET. These include:

- V<sub>IN</sub> to V<sub>OUT</sub> differential

- Output Current

- Case Size/Thermal Characteristics

- Gate Capacitance (C<sub>ISS</sub><10nF)

- Gate to Source threshold

The V<sub>IN(min)</sub> to V<sub>OUT</sub> ratio and current will determine the maximum  $R_{DSON}$  required. For example, for a 1.8V (±5%) to 1.5V conversion at 5A of load current, dropout voltage can be calculated as follows (using V<sub>IN(min)</sub>:

$$R_{DSON} = \frac{(V_{IN} - V_{OUT})}{I_{OUT}}$$

$$R_{DSON} = \frac{(1.71V - 1.5V)}{5A}$$

#### $R_{DSON} = 42m\Omega$

For performance reasons, we do not want to run the N-Channel in dropout. This will seriously affect transient response and PSRR (power supply ripple rejection). For this reason, we want to select a MOSFET that has lower than  $42m\Omega$  for our example application.

Size is another important consideration. Most importantly, the design must be able to handle the amount of power being dissipated.

The amount of power dissipated can be calculated as follows (using  $V_{\text{IN}(\text{max})})$ :

$$\begin{split} \mathsf{P}_{\mathsf{D}} &= (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{I}_{\mathsf{OUT}} \\ \mathsf{P}_{\mathsf{D}} &= (1.89\mathsf{V} - 1.5\mathsf{V}) \times \mathsf{5A} \\ \mathsf{P}_{\mathsf{D}} &= 1.95\mathsf{W} \end{split}$$

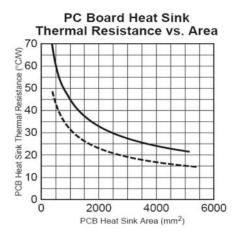

Now that we know the amount of power we will be dissipating, we will need to know the maximum ambient air temperature. For our case we're going to assume a maximum of 65°C ambient temperature, though different MOSFETs have different maximum operating junction temperatures. Most MOSFETs are rated to 150°C, while others are rated as high as 175°C. In this case, we're going to limit our maximum junction temperature to 125°C. The MIC5191 has no internal thermal protection for the MOSFET so it is important that the design provides margin for the maximum junction temperature. Our design will maintain better than 125°C junction temperature with 1.95W of power dissipation at an ambient temperature of 65°C. Our thermal resistance calculates as follows:

$$\theta_{JA} = \frac{T_J(max) - T_J(ambient)}{P_D}$$

$$\theta_{JA} = \frac{125^{\circ}C - 65^{\circ}C}{1.95W}$$

$\theta_{JA} = 31^{\circ}C/W$

So our package must have a thermal resistance less than 31°C /W. Table 1 shows a good approximation of power dissipation and package recommendation.

| Package                             | Power Dissipation |

|-------------------------------------|-------------------|

| TSOP-6                              | <850mW            |

| TSSOP-8                             | <950mW            |

| TSSOP-8                             | <1W               |

| PowerPAK™ 1212-8                    | <1.1W             |

| SO-8                                | <1.125W           |

| PowerPAK™ SO-8 D-Pack               | <1.4W             |

| TO-220/TO-263 (D <sup>2</sup> pack) | >1.4W             |

# Table 1. Power Dissipation and<br/>Package Recommendation

In our example, our power dissipation is greater than 1.4W, so we'll choose a TO-263 (D<sup>2</sup>Pack) N-Channel MOSFET.  $\theta_{JA}$  is calculated as follows:

$$\theta_{JA} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

Where  $\theta_{JC}$  is the junction to case resistance,  $\theta_{CS}$  is the case-to-sink resistance and the  $\theta_{SA}$  is the sink-to-ambient air resistance.

In the D<sup>2</sup> package we've selected, the  $\theta_{JC}$  is 2°C/W. The  $\theta_{CS}$ , assuming we are using the PCB as the heat sink, can be approximated to 0.2°C/W. This allows us to calculate the minimum  $\theta_{SA}$ :

$$\begin{split} \theta_{\text{SA}} &= \theta_{\text{JA}} - \theta_{\text{CS}} - \theta_{\text{JC}} \\ \theta_{\text{SA}} &= 31^{\circ}\text{C/W} - 0.2^{\circ}\text{C/W} - 2^{\circ}\text{C/W} \\ \theta_{\text{SA}} &= 28.8^{\circ}\text{C/W} \end{split}$$

Figure 8. PC Board Heat Sink

Another important characteristic is the amount of gate capacitance. Large gate capacitance can reduce transient performance by reducing the ability of the MIC5190 to slew the gate. It is recommended that the MOSFET used has an input capacitance <10nF ( $C_{ISS}$ ).

Source threshold specified in most MOSFET data sheets refers to the minimum voltage needed to fully enhance the MOSFET. Although for the most part, the MOSFET will be operating in the linear region and the  $V_{GS}$  (gate-

source voltage) will be less than the fully enhanced  $V_{GS}$ , it is recommended the VCC voltage has 2V over the

MIC5191

$$V_{CC1,2} \ge 2V + V_{CS} + V_{OUT}$$

saturation voltage of the MIC5191 output driver.

For our example, with a 1.5V output voltage, our MOSFET is fully enhanced at 4.5V<sub>GS</sub>, our V<sub>CC</sub> voltage should be greater or equal to 8V.

minimum  $V_{GS}$  and output voltage. This is due to the

#### **Input Capacitor**

Good input bypassing is important for improved performance. Low ESR and low ESL input capacitors reduce both the drain of the N-Channel MOSFET, as well as the source impedance to the MIC5191. When a load transient on the output occurs, the load step will also appear on the input. Deviations on the input voltage will be reduced by the MIC5191's PSRR, but nonetheless appear on the output. There is no minimum input capacitance, but for optimal performance it is recommended that the input capacitance be equal to or greater than the output capacitance.

#### **Output Capacitor**

The MIC5191 is stable with any type or value of output capacitor (even without any output capacitor!). This allows the output capacitor to select which parameters of the regulator are important. In cases where transient response is the most important, low ESR and low ESL ceramic capacitors are recommended. Also, the more capacitance on the output, the better the transient response.

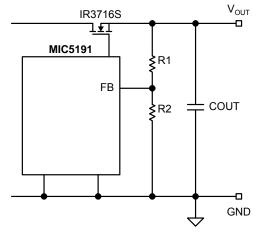

Figure 9. Post Regulator

Figure 10. Adjustable Output

The feedback resistors adjust the output to the desired voltage and can be calculated as follows:

$$V_{OUT} = V_{REF} \left( 1 + \frac{R1}{R2} \right)$$

$V_{\text{REF}}$  is equal to 1.0V for the MIC5191. The minimum output voltage (R1=0) is 0.5V. For output voltages less than 1V, use the MIC5190.The resistor tolerance adds error to the output voltage. These errors are accumulative for both R1 and R2. For example, our resistors selected have a  $\pm 1\%$  tolerance. This will contribute to a  $\pm 2\%$  additional error on the output voltage. The feedback resistors must also be small enough to allow enough current to the feedback node. Large feedback resistors will contribute to output voltage error.

$$V_{ERROR}$$

= R1 x 1<sub>FB</sub>

$V_{ERROR}$  = 1k $\Omega$  x 12µA

$V_{ERROR}$  = 12mV

For our example application, this will cause an increase in output voltage of 12mV. For the percentage increase,

$$V_{ERROR} \% = \frac{V_{ERROR}}{V_{OUT}} \times 100$$

$$V_{ERROR} \% = \frac{12mV}{1.5V} \times 100$$

$$V_{ERROR} \% = 0.8\%$$

By reducing R1 to  $100\Omega$ , the error contribution by the feed-back resistors and feedback current is reduced to less than 0.1%. This is the reason R1 should not be greater than  $100\Omega$ .

# Applying the MIC5191

#### Linear Regulator

The primary purpose of the MIC5191 is as a linear regulator, which enables an input supply voltage to drop down through the resistance of the pass element to a regulated output voltage.

#### Active Filter

Another application for the MIC5191 is as an active filter on the output of a switching regulator. This improves the power supply in several ways.

First, using the MIC5191 as a filter on the output can significantly reduce high frequency noise. Switching power supplies tends to create noise at the switching frequency in the form of a triangular voltage ripple. High frequency noise is also created by the high-speed switching transitions. A lot of time, effort, and money are thrown into the design of switching regulators to minimize these effects as much as possible. Figure 9 shows the MIC5191 as a post regulator.

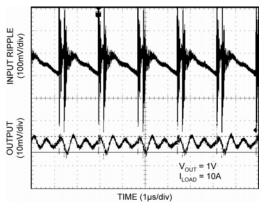

Figure 11. Ripple Reduction

Figure 11 shows the amount of ripple reduction for a 500 KHz switching regulator. The fundamental switching frequency is reduced from greater than 100mV to less than 10mV.

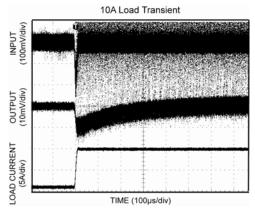

Figure 12. 10A Load Transient

The transient response also contributes to the overall AC output voltage deviation. Figure 12 shows a 1A to 10A load transient. The top trace is the output of the switching regulator (same circuit as Figure10). The output voltage undershoots by 100mV. Just by their topology, linear regulators have the ability to respond at much higher speeds than a switching regulator. Linear regulators do not have the limitation or restrictions of switching regulators which must reduce their bandwidth to less than their switching frequency.

Using the MIC5191 as a filter for a switching regulator reduces output noise due to ripple and high frequency switching noise. It also reduces undershoot (Figure 12) and over-shoot (Figure 13) due to load transients with decreased capacitance.

Figure 13. Transient Response

Due to the high DC gain (80dB) of the MIC5191, it also adds increased output accuracy and extremely high load regulation.

#### Distributed Power Supply

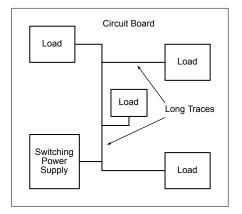

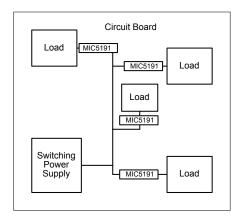

As technology advances and processes move to smaller and smaller geometries, voltage requirements go down and current requirements go up. This creates unique challenges when trying to supply power to multiple devices on a board. When there is one load to power, the difficulties are not quite as complex; trying to distribute power to multiple loads from one supply is much more problematic. If a large circuit board has multiple small-geometry ASICs, it will require the powering of multiple loads with its one power source. Assuming that the ASICs are dispersed throughout the board and that the core voltage requires a regulated 1V, Figure 14 shows the long traces from the power supply to the loads. Not only do we have to contend with the tolerance of the supply (line regulation, load regulation, output accuracy and temperature tolerances), but the trace lengths create additional issues with resistance and inductance. With lower voltages these parasitic values can easily bump the output voltage out of a usable tolerance.

Figure 14. Board Layout

But by placing multiple, small MIC5191 circuits close to each load, the parasitic trace elements caused by distance to the power supply are almost completely negated. By adjusting the switching supply voltage to 1.2V, for example, the MIC5191 will provide accurate 1V output, efficiently and with very little noise.

Figure 15. Improved Distributed Supplies

## **Package Information**

3.00 <sup>+0.10</sup> -0.10 E0.118 <sup>+0.004</sup>

10

4.90 [0.193] BSC

F  $\square$

NOTES: I. DIMENSIONS ARE IN MM LINGTES.

CONTROLLING DIMENSION: MM

DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.20 (0.008) PER SIDE.

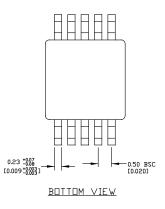

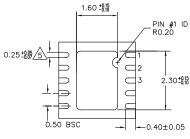

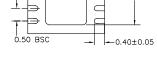

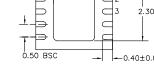

OPIN MSOP (N DIMENSIONS ARE IN MM [INCHES]. CONTROLLING DIMENSION: MM

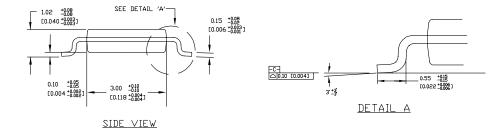

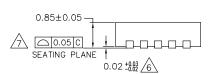

10-Pin MSOP (MM)

SIDE VIEW

NDTE: 1. ALL DIMENSIONS ARE IN MILLIMETERS. 2. MAX. PACKAGE WARPAGE IS 0.05 mm. 3. MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS. 4. PIN #1 ID ON TOP VILL BE LASER/INK MARKED. 5. DIMENSION APPLIES TO METALIZED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25 mm FROM TERMINAL TIP. 5. APPLIED DNLY FOR TERMINALS. 5. APPLIED CONCERNING NO. TOPMUMUM C

APPLIED FOR EXPOSED PAD AND TERMINALS.

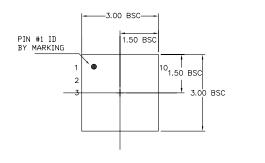

#### BOTTOM VIEW

10-Pin 3mm x 3mm MLF<sup>®</sup> (ML)

**4**.

a A

#### **MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA** TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2004 Micrel, Incorporated.