# CMX7032 CMX7042 AIS Data Processor

D/7032/42\_FI1.2/15 March 2018

# DATASHEET

**Provisional Issue**

# Marine AIS data processor designed for Limiter-Discriminator based RF systems

# Features:

- Half-Duplex GMSK and FSK Modem

- AIS and DSC Data Format

- Optimum Co-channel and Adjacent-channel Performance

- Flexible Channel Configuration:

- Two Simultaneous Rx

- One Tx

Support for:

Self Organising Time Division Multiple Access (SOTDMA)

Carrier-Sensing Channel Access (CSTDMA) Operation

- Low Profile 64 or 48 pad Leadless VQFN and 64 or 48 pin LQFP Packages

- Configurable by Function Image<sup>™</sup>

- Two RF Synthesisers (CMX7032 only)

- Two Auxiliary System Clock Generators

- Low-Power (3.0V to 3.6V) Operation

- Limiter-Discriminator Rx Interface

- Flexible Tx Interface: I/Q or Two-point Modulation

- Auxiliary ADC and DAC Functions - 4 x (10-bit) DACs

- 2 x (10-bit) ADCs

**Applications:**

- Automatic Identification System (AIS) for Marine Safety

- AIS Aids-To-Navigation (AtoN)

- AIS Class A and B Transponders

- AIS Rx-only or Tx-only Modules

# **1** Brief Description

The highly-integrated Baseband Signalling Processor ICs CMX7032 and CMX7042 fulfil the requirements of the Class A and Class B Marine Automatic Identification System (AIS) transponder market. The CMX7042 is identical in functionality to the CMX7032 with the exception that the two on-chip RF Synthesisers have been deleted, which enables it to be supplied in a smaller package. This document refers to both parts generically as the CMX7032/CMX7042, unless otherwise stated.

The AIS system allows ships and base stations to communicate their position and other data to each other without the need for a centralised controller. This allows vessels to "see" each other and take appropriate action to avoid collision and so improve marine safety. The system uses a GMSK 9600 baud data link in the Marine VHF radio band. The system requirements are defined in ITU-R M.1371-4.

The two channel access mechanisms used by AIS (Self Organising Time Division Multiple Access (SOTDMA) and Carrier-Sensing Time Division Multiple Access (CSTDMA)) are both supported by the CMX7032/CMX7042. Further information is given in section 6.2.

The CMX7032/CMX7042 devices utilise CML's proprietary *FirmASIC*<sup>®</sup> component technology. On-chip sub-systems are configured by a Function Image<sup>TM</sup>: this is a data file that is uploaded during device initialization which defines the device's function and feature set. The Function Image<sup>TM</sup> can be loaded automatically from an external serial memory or from a host µController over the built-in C-BUS serial interface. The device's functions and features can be enhanced by subsequent Function Image<sup>TM</sup> releases, facilitating in-the-field upgrades.

The CMX7032/CMX7042, when used with 7032/7042FI-1.x, is half duplex in operation, comprising two parallel Limiter-Discriminator Rx paths and one I/Q or two-point modulation Tx path. The Rx paths are configurable for AIS or DSC operation, the Tx for AIS only. The device performs signal modulation/demodulation with associated AIS functions, such as training sequence detection, NRZI conversion and HDLC processing (flags, bit stuffing/de-stuffing, CRC generate/check). Integrated Rx/Tx data buffers are also provided. This greatly reduces the processing requirements of the host  $\mu$ C. Provision of a number of auxiliary ADCs and DACs further simplifies the system hardware design, reducing the overall equipment cost and size.

This document refers specifically to the features provided by the CMX7032/CMX7042 Function Image™ FI-1.2.

This Datasheet is the first part of a two-part document comprising Datasheet and User Manual: the User Manual can be obtained by registering your interest in this product with your local CML representative.

# CONTENTS

| 1 | Brief       |                | ption                                  |    |  |  |  |  |

|---|-------------|----------------|----------------------------------------|----|--|--|--|--|

| - |             | ,              |                                        |    |  |  |  |  |

| 2 | Bloc        | k Diagr        | am                                     | 7  |  |  |  |  |

| 3 | Signal List |                |                                        |    |  |  |  |  |

|   | 3.1         |                | Definitions                            |    |  |  |  |  |

|   |             | U              |                                        |    |  |  |  |  |

| 4 | Reco        | ommeno         | ded External Components                | 12 |  |  |  |  |

| 5 | РСВ         | Layout         | Guidelines and Power Supply Decoupling | 15 |  |  |  |  |

| 6 | Gene        | eral Des       | scription                              | 17 |  |  |  |  |

|   | 6.1         |                | ew                                     |    |  |  |  |  |

|   | 6.2         | AIS sy         | stem formats                           | 18 |  |  |  |  |

| 7 | Detai       | iled De        | scriptions                             | 19 |  |  |  |  |

| • | 7.1         |                | Source                                 |    |  |  |  |  |

|   | 7.2         |                | nterface                               |    |  |  |  |  |

|   | 7.3         |                | on Image™ Load and Activation          |    |  |  |  |  |

|   | 7           | .3.1           | FI Loading from Host Controller        |    |  |  |  |  |

|   | 7           | .3.2           | FI Loading from Serial Memory          |    |  |  |  |  |

|   | 7.4         | Systen         | n Description and Tasks                | 24 |  |  |  |  |

|   |             | .4.1           | Signal Routing                         | 24 |  |  |  |  |

|   | 7           | .4.2           | Operating Modes                        | 24 |  |  |  |  |

|   | -           | .4.3           | Modem and Data Units                   |    |  |  |  |  |

|   |             | .4.4           | Timing and Synchronisation             |    |  |  |  |  |

|   | -           | .4.5           | Time of Arrival Reporting              |    |  |  |  |  |

|   | -           | .4.6           | Tx Timing                              |    |  |  |  |  |

|   |             | .4.7           | Rx Timing                              |    |  |  |  |  |

|   |             | .4.8           | CSTDMA Threshold Measurement.          |    |  |  |  |  |

|   |             | .4.9           | RSSI Measurement.                      |    |  |  |  |  |

|   | -           | .4.10          | RSSI Calibration                       |    |  |  |  |  |

|   | -           | .4.11          | ADCs                                   |    |  |  |  |  |

|   |             | .4.12          | DACs.                                  |    |  |  |  |  |

|   |             | .4.13<br>.4.14 | Interrupt Operation<br>Deep Sleep Mode |    |  |  |  |  |

|   |             |                | tion of Tasks                          |    |  |  |  |  |

|   |             | .5.1           | Tx Task Operation                      |    |  |  |  |  |

|   |             | .5.2           | Rx Task Operation                      |    |  |  |  |  |

|   |             | .5.3           | Registers and Buffers for Tx/Rx Tasks  |    |  |  |  |  |

|   |             | .5.4           | Write Data Registers                   |    |  |  |  |  |

|   |             | .5.5           | Read Data Registers                    |    |  |  |  |  |

|   | 7           | .5.6           | Data Tasks                             |    |  |  |  |  |

|   | 7           | .5.7           | Modem Tasks and Codes                  | 33 |  |  |  |  |

|   | 7.6         | Transr         | nission format                         |    |  |  |  |  |

|   | -           | .6.1           | Transmit Tasks                         |    |  |  |  |  |

|   |             | .6.2           | AIS Burst Mode Transmit                |    |  |  |  |  |

|   |             | .6.3           | Transmit Example                       |    |  |  |  |  |

|   |             | .6.4           | AIS Raw Mode Transmit                  |    |  |  |  |  |

|   |             | .6.5           | Transmitter Timing Control             |    |  |  |  |  |

|   |             | .6.6           | Modulation Formats                     |    |  |  |  |  |

|   | 7.7         | •              | tion                                   |    |  |  |  |  |

|   | 7           | .7.1           | AIS Burst Mode Receive                 | 39 |  |  |  |  |

|   | 7.7.2 AIS Raw Mode Receive                                                                                             |                                        |

|---|------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 7.7.3 DSC Receive                                                                                                      |                                        |

|   | 7.7.4 Receive Example                                                                                                  |                                        |

|   | 7.7.5 Rx Tasks                                                                                                         |                                        |

|   | 7.8 Configuration Tasks and Codes                                                                                      |                                        |

|   | 7.9 RF Synthesiser (CMX7032 only)                                                                                      |                                        |

|   | 7.10 System Clock Synthesisers                                                                                         |                                        |

|   | 7.11 Powersave                                                                                                         |                                        |

|   | 7.12 C-BUS Register Summary                                                                                            |                                        |

|   |                                                                                                                        |                                        |

|   |                                                                                                                        |                                        |

| 8 | Performance Specification                                                                                              |                                        |

| 8 | Performance Specification           8.1         Electrical Performance                                                 |                                        |

| 8 | 8.1 Electrical Performance                                                                                             | 51                                     |

| 8 | 8.1 Electrical Performance<br>8.1.1 Absolute Maximum Ratings                                                           | 51<br>51                               |

| 8 | <ul> <li>8.1 Electrical Performance</li> <li>8.1.1 Absolute Maximum Ratings</li> <li>8.1.2 Operating Limits</li> </ul> | 51<br>51<br>52                         |

| 8 | <ul> <li>8.1 Electrical Performance</li></ul>                                                                          |                                        |

| 8 | <ul> <li>8.1 Electrical Performance</li></ul>                                                                          | 51<br>51<br>52<br>53<br>53<br>57       |

| 8 | <ul> <li>8.1 Electrical Performance</li></ul>                                                                          | 51<br>51<br>52<br>53<br>53<br>57<br>58 |

| 8 | <ul> <li>8.1 Electrical Performance</li></ul>                                                                          | 51<br>51<br>52<br>53<br>57<br>58<br>59 |

# TABLES

| Table 1 Definition of Power Supply and Reference Voltages | 11 |

|-----------------------------------------------------------|----|

| Table 2 Component Values                                  | 14 |

| Table 3 BOOTEN Pin States                                 | 21 |

| Table 4 Data Tasks                                        | 32 |

| Table 5 Modem Tasks                                       | 33 |

| Table 6 AIS Burst Transmit Example                        | 35 |

| Table 7 Tx Sequence Events                                | 36 |

| Table 8 Example Tx Event Sequence Setup (Class B)         | 37 |

| Table 9 Example Tx Event Sequence Setup (Class A)         | 38 |

| Table 10 AIS Burst Receive Example                        | 43 |

| Table 11 Configuration Tasks                              | 44 |

| Table 12 C-BUS Registers                                  | 50 |

# FIGURES

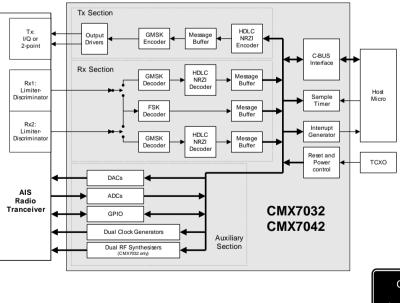

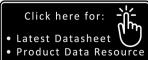

| Figure 1  | CMX7032/CMX7042 Block Diagram                    | 7  |

|-----------|--------------------------------------------------|----|

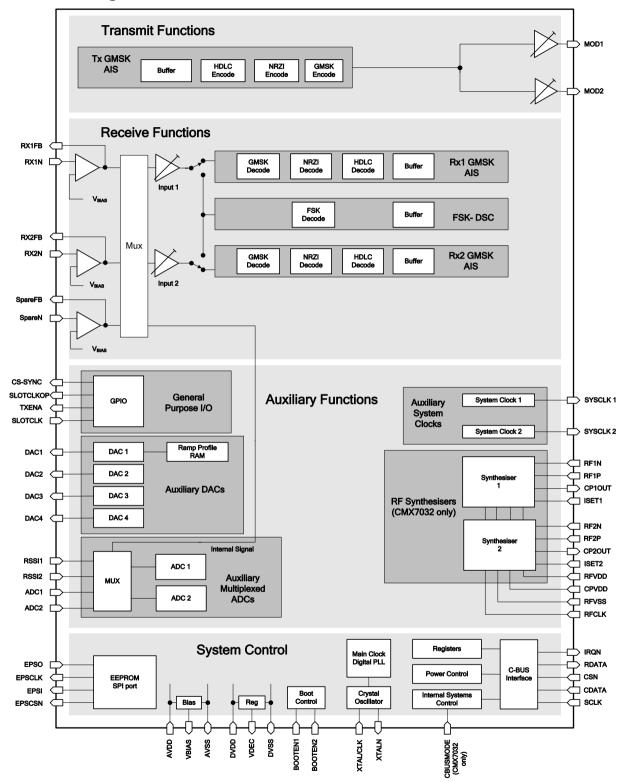

| Figure 2  | CMX7032 Recommended External Components          | 12 |

| Figure 3  | CMX7042 Recommended External Components          | 13 |

| Figure 4  | CMX7032 Power Supply Connections and De-coupling | 15 |

| Figure 5  | CMX7042 Power Supply Connections and De-coupling | 16 |

| Figure 6  | C-BUS Transactions                               | 19 |

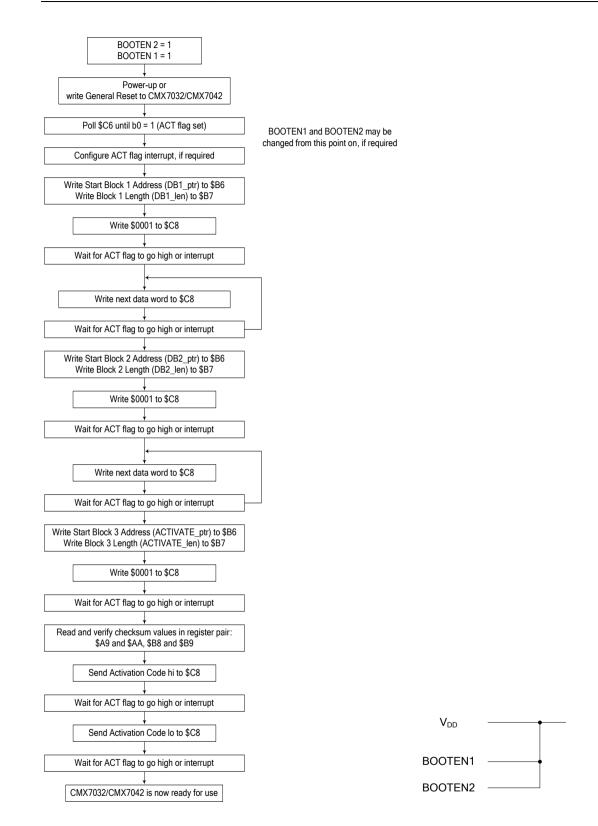

| Figure 7  | FI Loading from Host                             | 22 |

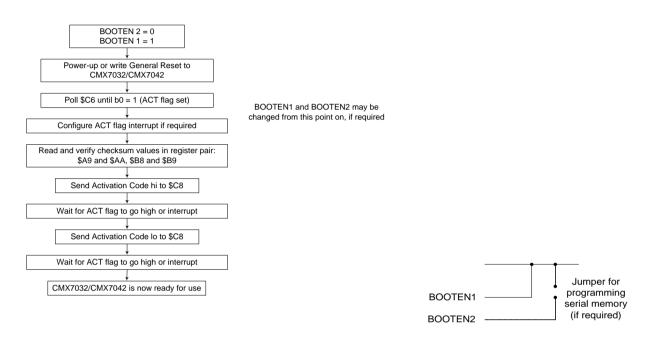

| Figure 8  | FI Loading from Serial Memory                    | 23 |

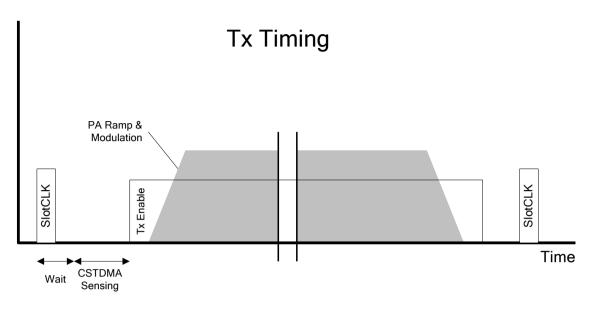

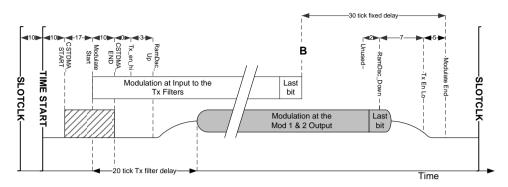

| Figure 9  | Tx Burst Timing                                  | 26 |

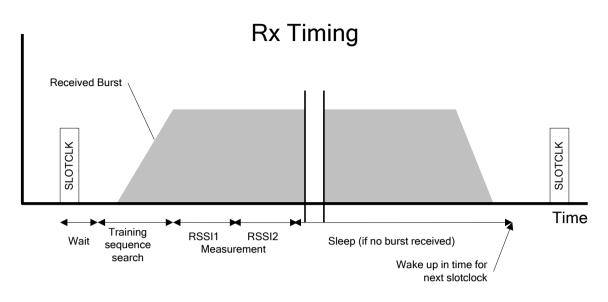

| Figure 10 | ) Rx Burst Timing                                | 27 |

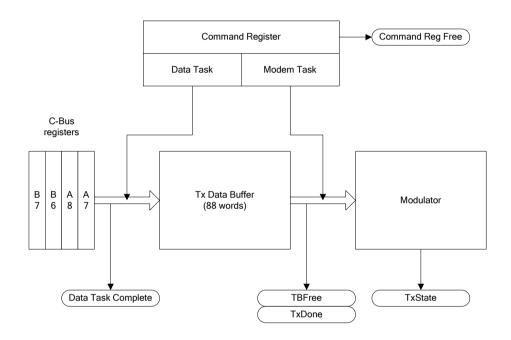

| Figure 11 | Tx Task Operation                                        | . 29 |

|-----------|----------------------------------------------------------|------|

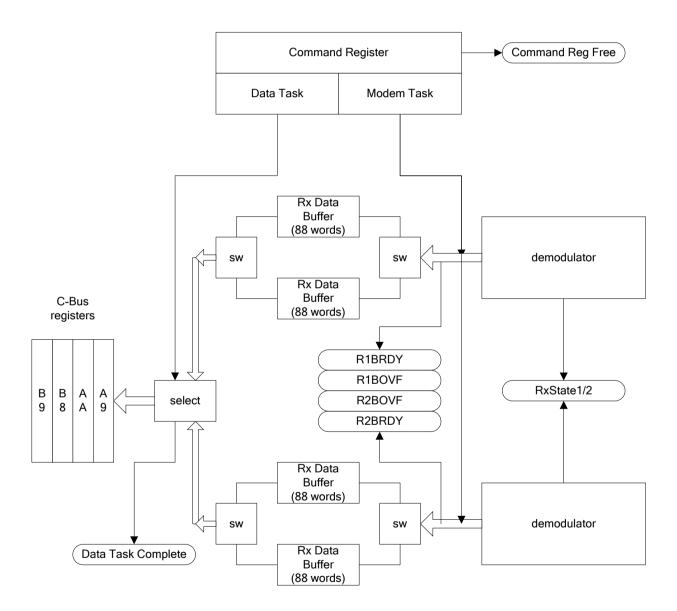

| Figure 12 | Rx Task Operation                                        | . 30 |

| Figure 13 | Typical AIS Transmission                                 | . 37 |

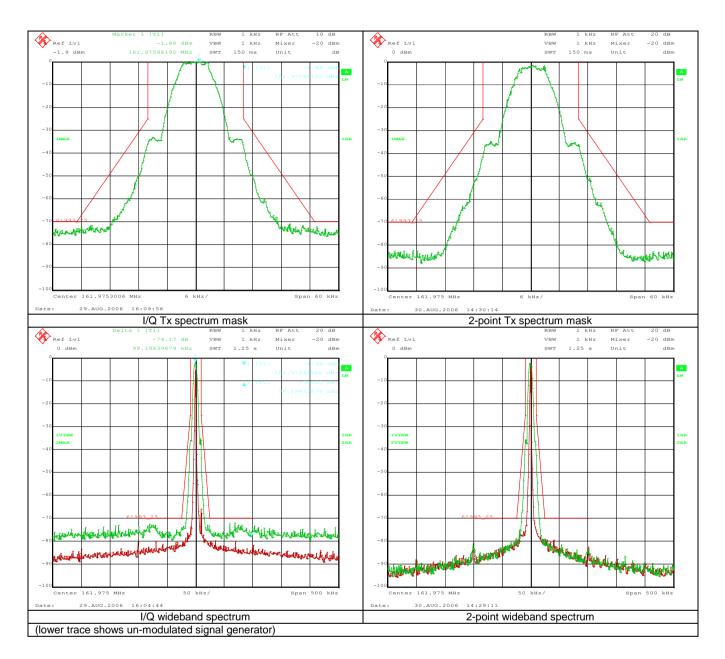

| Figure 14 | Tx Spectrum Masks                                        | . 39 |

| Figure 15 | DSC Format                                               | . 42 |

| Figure 16 | Example RF Synthesiser Components                        | . 45 |

|           | Single RF PLL Block Diagram                              |      |

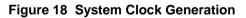

| Figure 18 | System Clock Generation                                  | . 48 |

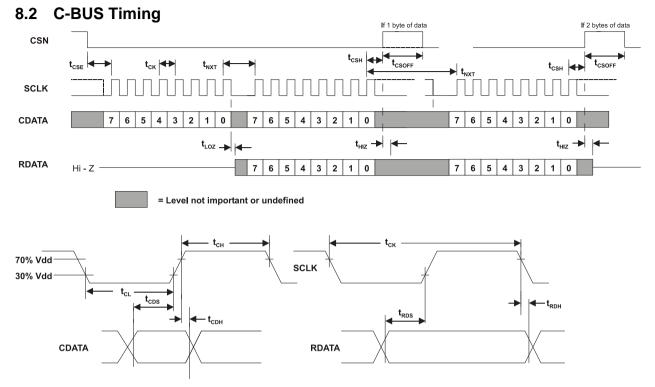

| Figure 19 | C-BUS Timing                                             | . 58 |

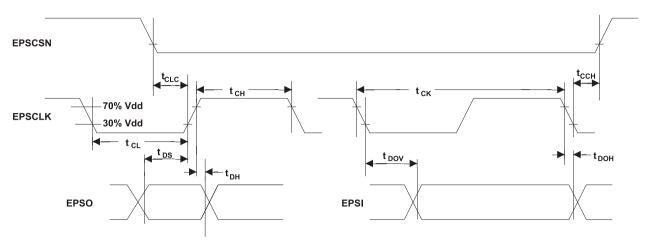

| Figure 20 | SPI Interface Timing                                     | . 59 |

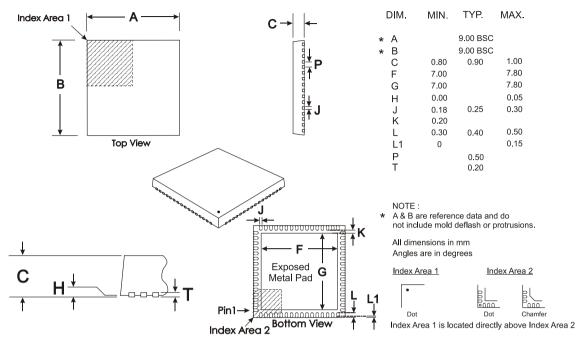

| Figure 21 | Mechanical Outline for 64-pad VQFN Package (Q1)          | . 60 |

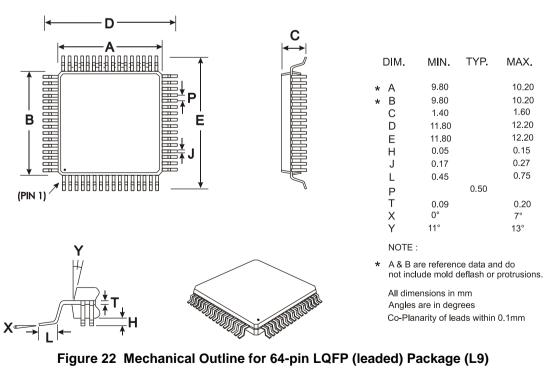

| Figure 22 | Mechanical Outline for 64-pin LQFP (leaded) Package (L9) | . 60 |

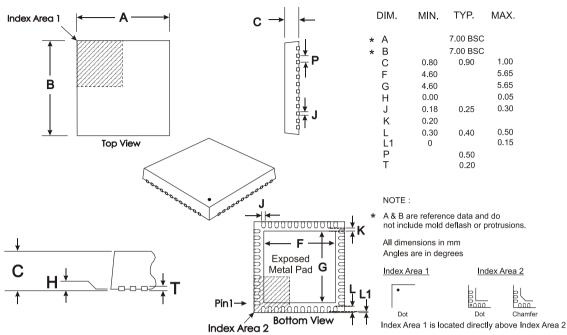

| Figure 23 | Mechanical Outline for 48-pad VQFN Package (Q3)          | . 61 |

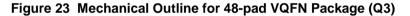

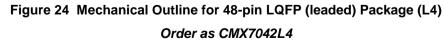

| Figure 24 | Mechanical Outline for 48-pin LQFP (leaded) Package (L4) | . 61 |

|           |                                                          |      |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

# 1.1 History

| Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Date     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 15      | <ul> <li>Section 10.1: added exactTrax selection options for FI-3.x</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27/03/18 |

| 14      | <ul> <li>Section 7.6.5: new table added for example Class A Tx event sequence setup</li> <li>Section 8.1.3: corrections to typical figures for analogue supply current in Deep Sleep mode and digital supply current for a System Clock. Explanatory notes added at the end of this section.</li> <li>Section 9.19.2.2: bit table modified to state that all values other than those stated are reserved.</li> <li>Section 9.19.2.12: Information added to describe disabling analogue functionality</li> </ul> | 10/01/15 |

|         | to decrease current consumption in Deep Sleep mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|         | Minor style changes and correction of typographical errors                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 13      | <ul> <li>Section 7.6.5 rewritten to correct transmit timing control description</li> <li>New Figure 13 showing typical AIS transmission</li> <li>Section 9.19, modem task table, Tx AIS unscheduled – TDB - bit 5 corrected.</li> <li>Section 9.19, sub-paragraph levels restructured to improve clarity</li> <li>Minor style changes and correction of typographical errors</li> </ul>                                                                                                                         | 21/11/12 |

| 12      | <ul> <li>Add CRC disable feature.</li> <li>Add CS-Sync output.</li> <li>Add SlotCLK output.</li> <li>Changed EEPROM references to serial memory</li> </ul>                                                                                                                                                                                                                                                                                                                                                      | 07/10/11 |

| 11      | <ul> <li>Update to RF Synthesiser paramaters, following evaluation.</li> <li>Correction of errors in \$C8 Command Register Table.</li> <li>Further Information on Status2 (\$C5) Register.</li> <li>Clarification of BOOTEN options by Table 13 and Table 3.</li> <li>Correction of error in Figure 8.</li> <li>Update to Modulation Notes (section 11.1) and clarification of Figure 26.</li> </ul>                                                                                                            | 29/7/11  |

| 10      | <ul> <li>Addition of operating voltage range clarification (3.0V to 3.6V) into History files</li> <li>Addition of revised Function Image<sup>™</sup> flowcharts (Fig 7 and 8) into History files</li> </ul>                                                                                                                                                                                                                                                                                                     | 18/9/09  |

|   |                                                                                   | 1        |

|---|-----------------------------------------------------------------------------------|----------|

| 9 | <ul> <li>Correction to HCT in Task table: should be \$2E not \$0E</li> </ul>      | 11/9/09  |

|   | HCT \$A7 settings removed from Modem Task table. This information is present      |          |

|   | in the table immediately below.                                                   |          |

|   | Addition of update to register \$CE b8 description into History files             |          |

|   | Remove ac coupling from component diagrams - should always be dc coupled          |          |

|   | <ul> <li>Clarification of the power-up and reset conditions</li> </ul>            |          |

|   | Addition of a hyperlinked table in section 10, in place of C-BUS Register Map     |          |

|   | Minor style changes and correction of typographical errors                        |          |

| 8 | NRZI encoder re-initialised on every Tx burst.                                    | 15/6/09  |

|   | Slot initialization range corrected from 2250 to 2249                             |          |

|   | • Modem tasks table in section 11.18 corrected (Tx AIS raw / Tx AIS unscheduled)  |          |

|   | Table 1 Note 6 clarified.                                                         |          |

| 7 | C-BUS names standardised                                                          | 13/05/09 |

|   | AuxADC and AuxDAC changed to ADC and DAC                                          |          |

|   | SpareADC changed to Spare                                                         |          |

|   | Standards references updated                                                      |          |

|   | • Slot Counter and ToA compensation and description added: 7.4.5, 7.7.5, table 10 |          |

|   | RSSI1 & 2 periods shown separately in fig 10                                      |          |

|   | Contact details updated                                                           |          |

| 6 | Addition of C-BUS Mode pin (CMX7032 only), omitted from version 5.                | 4/12/08  |

|   | Clarification of operation of DSC Raw and Formatted Modes.                        |          |

|   | Clarification of RF PLL description: 'channel' replaced by 'PLL'.                 |          |

|   | Updated parametric figures, based on device characterisation.                     |          |

|   | Corrections and updates to C-BUS Register Map.                                    |          |

|   | Addition of DSC Format Enable flag into Command register (\$C8) bit 6.            |          |

|   | • Section 9.19.2.7 clarification: 'polarity' should refer to the 'initial state'. |          |

|   | Correction of typographical errors and incorrect hyperlinks.                      |          |

| 5 | Original document, prepared for release of FI-1.2.1.1                             | 14/1/08  |

|   |                                                                                   |          |

# 2 Block Diagram

Figure 1 CMX7032/CMX7042 Block Diagram

# 3 Signal List

| ာ ၁၊ပို                | jnai List |                |      |                                                                                                                                                                                                                          |  |  |

|------------------------|-----------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CMX70<br>64-pi<br>Q1/L | n 48-pin  | Signal<br>Name | Туре | Description                                                                                                                                                                                                              |  |  |

| 1                      | 8         | IRQN           | OP   | C-BUS: A 'wire-ORable' output for connection to the Interrupt Request input of the host. Pulled down to $\text{DV}_{SS}$ when active and is high impedance when inactive. An external pull-up resistor (R1) is required. |  |  |

| 2                      | -         | RF1N           | IP   | RF Synthesiser #1 Negative input.                                                                                                                                                                                        |  |  |

| 3                      | -         | RF1P           | IP   | RF Synthesiser #1 Positive input.                                                                                                                                                                                        |  |  |

| 4                      | -         | RFVSS          | PWR  | The negative supply rail (ground) for the RF synthesisers.                                                                                                                                                               |  |  |

| 5                      | -         | CP1OUT         | OP   | 1st Charge Pump output.                                                                                                                                                                                                  |  |  |

| 6                      | -         | ISET1          | IP   | 1st Charge Pump Current Set input.                                                                                                                                                                                       |  |  |

| 7                      | -         | RFVDD          | PWR  | The 2.5V positive supply rail for the RF synthesisers. This should be decoupled to $\text{RFV}_{SS}$ by a capacitor mounted close to the device pins.                                                                    |  |  |

| 8                      | -         | RF2N           | IP   | RF Synthesiser #2 Negative input.                                                                                                                                                                                        |  |  |

| 9                      | -         | RF2P           | IP   | RF Synthesiser #2 Positive input.                                                                                                                                                                                        |  |  |

| 10                     | -         | RFVSS          | PWR  | The negative supply rail (ground) for the 2nd RF synthesiser.                                                                                                                                                            |  |  |

| 11                     | -         | CP2OUT         | OP   | 2nd Charge Pump output.                                                                                                                                                                                                  |  |  |

| 12                     | -         | ISET2          | IP   | 2nd Charge Pump Current Set input.                                                                                                                                                                                       |  |  |

| 13                     | -         | CPVDD          | PWR  | The 3.3V positive supply rail for the RF charge pumps. This should be decoupled to $\text{RFV}_{SS}$ by a capacitor mounted close to the device pins.                                                                    |  |  |

| 14                     | -         | RFCLK          | IP   | RF Clock Input (common to both synthesisers) <sup>1</sup> .                                                                                                                                                              |  |  |

| 15                     | -         | CS-SYNC        | OP   | Pulse output when device is about to Tx.                                                                                                                                                                                 |  |  |

| 16                     | -         | SLOTCLKOP      | OP   | Internal SlotCLK output                                                                                                                                                                                                  |  |  |

| 17                     | -         | ET VCO ENA     | OP   | FI-3 only – TxVCO enable in exactTrax mode                                                                                                                                                                               |  |  |

| 18                     | 9         | VDEC           | PWR  | Internally generated 2.5V digital supply voltage. Must be decoupled to $DV_{SS}$ by capacitors mounted close to the device pins. No other connections allowed, except for optional connection to $RFV_{DD}$ .            |  |  |

| 19                     | 10        | SLOTCLK        | IP   | Slot Clock from host (37.5Hz).                                                                                                                                                                                           |  |  |

| -                      | 11        | CS-SYNC        | OP   | Pulse output when device is about to Tx.                                                                                                                                                                                 |  |  |

| -                      | 12        | SLOTCLKOP      | OP   | Internal SlotCLK output                                                                                                                                                                                                  |  |  |

| 20                     | 13        | SYSCLK1        | OP   | Synthesised Digital System Clock Output 1.                                                                                                                                                                               |  |  |

| 21                     | 14        | DVSS           | PWR  | Digital Ground.                                                                                                                                                                                                          |  |  |

| 22                     | -         | -              | NC   | Reserved – do not connect this pin.                                                                                                                                                                                      |  |  |

| 23                     | 15        | TXENA          | OP   | Enable for external Tx hardware.                                                                                                                                                                                         |  |  |

<sup>&</sup>lt;sup>1</sup> To minimise crosstalk, this signal should be connected to the same clock source as XTAL/CLK input. By default, this is connected internally at power-on, alternatively, this may be achieved by connecting the pin to the XTALN output when a 19.2MHz source is in use.

| CMX7032<br>64-pin<br>Q1/L9 | CMX7042<br>48-pin<br>Q3/L4 | Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                        |  |  |

|----------------------------|----------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 24                         | 16                         | RX1N           | IP   | Rx1 inverting input.                                                                                                                                                                                                                                               |  |  |

| 25                         | 17                         | RX1FB          | OP   | Rx1 input amplifier feedback.                                                                                                                                                                                                                                      |  |  |

| 26                         | 18                         | RX2N           | IP   | Rx2 inverting input.                                                                                                                                                                                                                                               |  |  |

| 27                         | 19                         | RX2FB          | OP   | Rx2 input amplifier feedback.                                                                                                                                                                                                                                      |  |  |

| 28                         | 20                         | SpareFB        | OP   | Spare input amplifier feedback.                                                                                                                                                                                                                                    |  |  |

| 29                         | 21                         | SpareN         | IP   | Spare inverting input.                                                                                                                                                                                                                                             |  |  |

| 30                         | 22                         | AVSS           | PWR  | Analogue Ground.                                                                                                                                                                                                                                                   |  |  |

| 31                         | 23                         | MOD1           | OP   | Modulator 1 output.                                                                                                                                                                                                                                                |  |  |

| 32                         | 24                         | MOD2           | OP   | Modulator 2 output.                                                                                                                                                                                                                                                |  |  |

| 33                         | 25                         | VBIAS          | OP   | Internally generated bias voltage of about $AV_{DD}/2$ , except when the device is in 'Powersave' mode when $V_{BIAS}$ will discharge to $AV_{SS}$ . Must be decoupled to $AV_{SS}$ by a capacitor mounted close to the device pins. No other connections allowed. |  |  |

| 34                         | 26                         | -              | NC   | Reserved – do not connect this pin.                                                                                                                                                                                                                                |  |  |

| 35                         | 27                         | RSSI1          | IP   | Analogue RSSI input from Limiter / Discriminator 1.                                                                                                                                                                                                                |  |  |

| 36                         | 28                         | RSSI2          | IP   | Analogue RSSI input from Limiter / Discriminator 2.                                                                                                                                                                                                                |  |  |

| 37                         | 29                         | ADC1           | IP   | ADC input 1.                                                                                                                                                                                                                                                       |  |  |

| 38                         | 30                         | ADC2           | IP   | ADC input 2.                                                                                                                                                                                                                                                       |  |  |

| 39                         | 31                         | AVDD           | PWR  | Analogue +3.3V supply rail. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to $AV_{SS}$ by capacitors mounted close to the device pins.                                                                    |  |  |

| 40                         | 32                         | DAC1           | OP   | DAC output 1/RAMDAC.                                                                                                                                                                                                                                               |  |  |

| 41                         | 33                         | DAC2           | OP   | DAC output 2.                                                                                                                                                                                                                                                      |  |  |

| 42                         | 34                         | AVSS           | PWR  | Analogue Ground.                                                                                                                                                                                                                                                   |  |  |

| 43                         | 35                         | DAC3           | OP   | DAC output 3.                                                                                                                                                                                                                                                      |  |  |

| 44                         | 36                         | DAC4           | OP   | DAC output 4.                                                                                                                                                                                                                                                      |  |  |

| -                          | 37                         | DVSS           | PWR  | Digital Ground.                                                                                                                                                                                                                                                    |  |  |

| 45                         | 38                         | VDEC           | PWR  | Internally generated 2.5V supply voltage. Must be decoupled to DV <sub>SS</sub> by capacitors mounted close to the device pins. No other connections allowed, except for the optional connection to RFV <sub>DD</sub> .                                            |  |  |

| 46                         | 39                         | XTAL/CLK       | IP   | 19.2MHz input from the external clock source or 9.6MHz Xtal.                                                                                                                                                                                                       |  |  |

| 47                         | 40                         | XTALN          | OP   | The output of the on-chip 9.6MHz Xtal oscillator inverter. NC if 19.2MHz Clock used.                                                                                                                                                                               |  |  |

| 48                         | 41                         | DVDD           | PWR  | Digital +3.3V supply rail. This pin should be decoupled to $DV_{SS}$ by capacitors mounted close to the device pins.                                                                                                                                               |  |  |

| 49                         | 42                         | CDATA          | IP   | C-BUS: Command Data. Serial data input from the $\mu$ C.                                                                                                                                                                                                           |  |  |

| CMX7032<br>64-pin<br>Q1/L9 | CMX7042<br>48-pin<br>Q3/L4 | Signal<br>Name | Туре  | Description                                                                                                                                                                        |  |  |

|----------------------------|----------------------------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 50                         | 43                         | RDATA          | TS OP | C-BUS: Reply Data. A 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                          |  |  |

| 51                         | 44                         | -              | NC    | Reserved – do not connect this pin.                                                                                                                                                |  |  |

| 52                         | 45                         | DVSS           | PWR   | Digital Ground.                                                                                                                                                                    |  |  |

| 53                         | -                          | -              | NC    | Reserved – do not connect this pin.                                                                                                                                                |  |  |

| 54                         | 46                         | SCLK           | IP    | C-BUS: The C-BUS serial clock input from the $\mu$ C.                                                                                                                              |  |  |

| 55                         | 47                         | SYSCLK2        | OP    | Synthesised Digital System Clock Output 2.                                                                                                                                         |  |  |

| 56                         | 48                         | CSN            | IP    | C-BUS: The C-BUS chip select input from the $\mu$ C.                                                                                                                               |  |  |

| 57                         | -                          | CBUSMODE       | IP+PD | Reserved – connect to DV <sub>SS</sub> (CMX7032 only).                                                                                                                             |  |  |

| 58                         | 1                          | EPSI           | OP    | Serial Memory Interface:SPI bus Output.                                                                                                                                            |  |  |

| 59                         | 2                          | EPSCLK         | OP    | Serial Memory Interface:SPI bus Clock.                                                                                                                                             |  |  |

| 60                         | 3                          | EPSO           | IP+PD | Serial Memory Interface:SPI bus Input.                                                                                                                                             |  |  |

| 61                         | 4                          | EPSCSN         | OP    | Serial Memory Interface:SPI bus Chip Select.                                                                                                                                       |  |  |

| 62                         | 5                          | BOOTEN1        | IP+PD | Used in conjunction with BOOTEN2 to determine the operation of the bootstrap program.                                                                                              |  |  |

| 63                         | 6                          | BOOTEN2        | IP+PD | Used in conjunction with BOOTEN1 to determine the operation of the bootstrap program.                                                                                              |  |  |

| 64                         | 7                          | DVSS           | PWR   | Digital Ground.                                                                                                                                                                    |  |  |

| Exposed<br>Metal<br>Pad    | Exposed<br>Metal<br>Pad    | SUB            | ~     | On Q1 and Q3 packages only, the central metal pad may be connected to Analogue Ground (AV <sub>SS</sub> ) or left unconnected. <b>No other electrical connection is permitted.</b> |  |  |

### Notes:

IP

OP

NC

= Input (+PU/PD = internal pullup/pulldown resistor)

= Output

TS OP = 3-state Output

PWR = Power Supply Connection

= No Connection

Functions with no associated pin number are not available in the CMX7042.

SLOTCLKOP and CS-SYNC functions are not available on CMX7032 devices with batch codes before #72181.

# 3.1 Signal Definitions

| Signal<br>Name    | Pins  | Usage                                                                           |

|-------------------|-------|---------------------------------------------------------------------------------|

| AV <sub>DD</sub>  | AVDD  | Power supply for analogue circuits                                              |

| DV <sub>DD</sub>  | DVDD  | Power supply for digital circuits                                               |

| RFV <sub>DD</sub> | RFVDD | Power supply for RF synthesiser circuits                                        |

| CPV <sub>DD</sub> | CPVDD | Power supply for RF charge pump                                                 |

| V <sub>DEC</sub>  | VDEC  | Power supply for core logic, derived from DV <sub>DD</sub> by on-chip regulator |

| V <sub>BIAS</sub> | VBIAS | Internal analogue reference level, derived from AV <sub>DD</sub>                |

| AV <sub>SS</sub>  | AVSS  | Ground for all analogue circuits                                                |

| DV <sub>SS</sub>  | DVSS  | Ground for all digital circuits                                                 |

| RFV <sub>SS</sub> | RFVSS | Ground for all RF circuits                                                      |

# Table 1 Definition of Power Supply and Reference Voltages

# 4 Recommended External Components

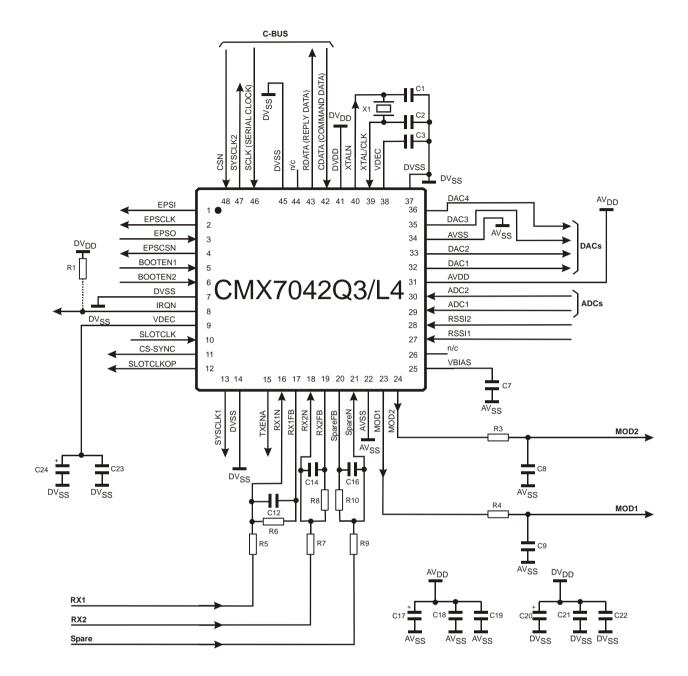

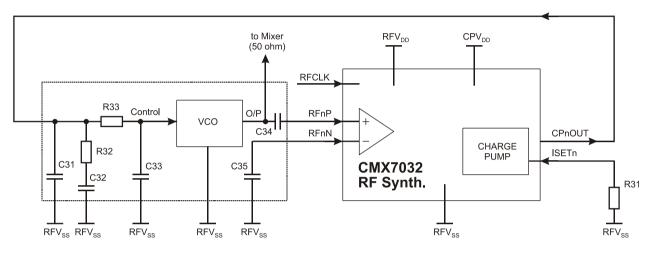

Figure 2 CMX7032 Recommended External Components

Figure 3 CMX7042 Recommended External Components

#### **Table 2 Component Values**

| R6        | 100kΩ<br>100kΩ<br>100kΩ<br>See note 2<br>100kΩ<br>See note 3<br>100kΩ | C1<br>C2<br>C3<br>C4<br>C7<br>C8<br>C9 | 10nF<br><i>not fitted</i><br>100nF<br>100pF | C16<br>C17<br>C18<br>C19<br>C20<br>C21<br>C22 | 10nF<br>10nF<br>10μF<br>10nF |    | 10nF<br>10µF<br>10nF<br>10µF<br>10nF<br>10µF |

|-----------|-----------------------------------------------------------------------|----------------------------------------|---------------------------------------------|-----------------------------------------------|------------------------------|----|----------------------------------------------|

| R9<br>R10 | See note 4<br>100kΩ                                                   |                                        | 100pF<br>100pF<br>100pF                     | 022                                           | IUIF                         | X1 | 9.6MHz<br>See note 1                         |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

Notes:

- 1. X1 can be a 9.6MHz crystal or a 19.2MHz external clock generator. The tracks between the crystal and the device pins should be as short as possible to achieve maximum stability and best start up performance.

- 2. R5 should be selected to provide the desired dc gain (assuming C11 is not present) of the input, as follows:

### $|GAIN_{RX1N}| = 100k\Omega / R5$

The gain should be such that the resultant output at the RX1FB pin is within the input signal range specified in 8.1.3.

3. R7 should be selected to provide the desired dc gain (assuming C13 is not present) of the input as follows:

$$|\text{GAIN}_{\text{RX2N}}| = 100 \text{k}\Omega / \text{R7}$$

The gain should be such that the resultant output at the RX2FB pin is within the input signal range specified in 8.1.3.

4. R9 should be selected to provide the desired dc gain (assuming C15 is not present) of the input as follows:

$$|GAIN_{SpareN}| = 100k\Omega / R9$$

The gain should be such that the resultant output at the SpareFB pin is within the input signal range specified in 8.1.3.

- 5. Care should be taken in connecting the output of the Limiter-Discriminator device to the Rx input pins of the CMX7032. The format of the GMSK signal requires that the frequency response of the input circuits extends to below 10Hz, however the variations in the incoming AIS signals from many different stations require that the input must rapidly follow the changes in dc and signal levels without de-grading the signal seen at the Rx input pins.

- 6. A single 10μF electrolytic capacitor (C24, fitted as shown) may be used for smoothing the power supply to both V<sub>DEC</sub> pins, providing they are connected together on the pcb with an adequate width power supply trace. Alternatively, separate smoothing capacitors should be connected to each V<sub>DEC</sub> pin. High frequency decoupling capacitors (C3 and C23) must always be fitted as close as possible to both V<sub>DEC</sub> pins.

# 5 PCB Layout Guidelines and Power Supply Decoupling

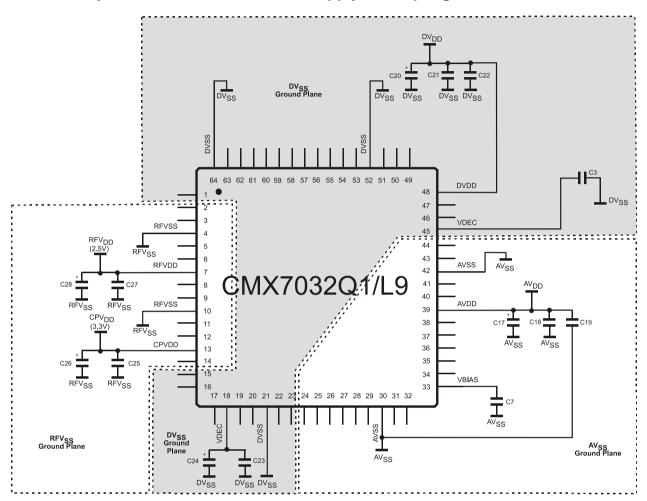

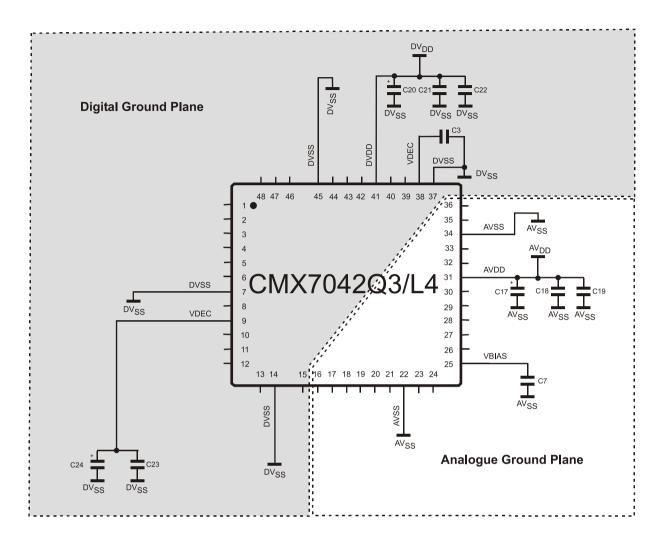

Figure 4 CMX7032 Power Supply Connections and De-coupling

Component Values as per Table 2.

#### Figure 5 CMX7042 Power Supply Connections and De-coupling

#### Component Values as per Table 2.

#### Notes:

- It is important to protect the analogue pins from extraneous inband noise and to minimise the impedance between the CMX7032 and the supply and bias de-coupling capacitors. The supply decoupling capacitors should be as close as possible to the CMX7032. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the AV<sub>SS</sub>, RFV<sub>SS</sub> and DV<sub>SS</sub> supplies in the area of the CMX7032, with provision to make links between them, close to the CMX7032. Use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers.

- 2. The central metal pad (which is exposed on Q1 and Q3 packages only) may be electrically unconnected or, alternatively, may be connected to Analogue Ground (AV<sub>SS</sub>). No other electrical connection is permitted.

- 3. V<sub>BIAS</sub> is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled to ensure its integrity so, apart from the decoupling capacitor shown, no other loads should be connected. If V<sub>BIAS</sub> needs to be used to set the discriminator mid-point reference, it must be buffered with an external high input impedance buffer.

- The 2.5V V<sub>DEC</sub> output can be used to supply the 2.5V RFV<sub>DD</sub>, to remove the need for an external 2.5V regulated supply. VDEC can be directly connected to RFVDD.

# 6 General Description

# 6.1 Overview

# **Tx Modem Functions**

- AIS 25kHz channel (GMSK, 9600bps, 2.4kHz deviation, BT = 0.4)

- AIS Burst mode with full AIS frame formatting (HDLC-type)

- Bit stuffing

- NRZI coding

- Training sequence and start/stop flag insertion

- CRC generation

- AIS Raw mode (for greater flexibility)

- o Supports arbitrary data streams for user-defined protocols

- Full support for the AIS Class B carrier-sensing channel access scheme (CSTDMA)

- Full support for the AIS Class B Self-organising TDMA access scheme

- 160 byte (equivalent to 5 AIS slots) Tx data buffer

- Flexible Tx Interface

- o Two-point modulation outputs, with independent gain and polarity controls

- I/Q modulation outputs, for use with an I/Q upconverter

- CS-SYNC output to facilitate IEC 62287-1 testing

#### **Rx Modem Functions**

- Configurable modulation format:

- AIS 25kHz channel (GMSK, 9600bps, 2.4kHz deviation, BT = 0.4)

- DSC (de-emphasised FSK, 1200bps)

- Simultaneous reception of two AIS channels, or one AIS and one DSC channel

- AIS Burst mode with full AIS frame formatting (HDLC-type)

- Frame sync recognition

- o Bit de-stuffing

- o NRZI decoding

- Training sequence and start/stop flag detection

- CRC checking

- AIS Raw mode (for greater flexibility)

- Supports arbitrary data streams for user-defined protocols

- DSC reception

- Raw mode

- o Formatted mode

- Four 160-byte Rx data buffers can automatically store up to four 5-slot AIS bursts (2 per Rx channel)

- Rx signal input gain and polarity controls

- Time-of-arrival reporting assists with timekeeping in the absence of GPS

- Option to report messages with CRC errors

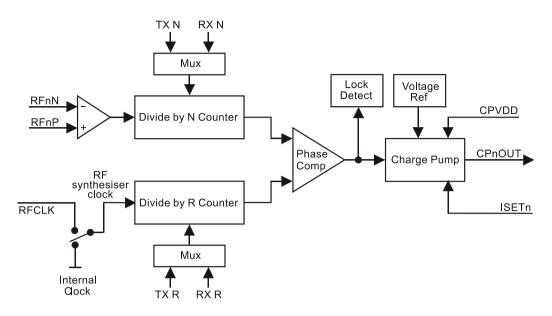

# 100 - 600 MHz RF Synthesisers (CMX7032 only)

- Two Integer-N synthesisers

- Flexible design minimises reference spurs for low phase noise results

- Charge pump

- High/low soft selectable current setting to speed large frequency channel changes

- Nominal current user defined by external resistor value

- Lock detect

<sup>© 2018</sup> CML Microsystems Plc

#### Analog I/O Functions

- Auxiliary ADC system

- Two 10-bit successive approximation ADCs with integrated sample and hold

- One AuxADC is dedicated to RSSI measurement in a user defined window, the other is available for general use

- Ramping auxiliary DAC

- DAC sequences through a user-configured sequence of DAC output values to develop a specific rising/falling DAC output signal. This is useful for ramping an RF PA, and can be configured to happen automatically at the start and end of a burst.

- Can operate as a general purpose DAC, if desired

- Three general purpose auxiliary DACs

#### **System Functions**

- All internal subsystems are controlled via a single serial host interface to reduce host µC pin count and simplify external host driver complexity.

- Transaction oriented command/response logical host interface executes tasks supporting normal

operation, device configuration, and functions to assist manufacturing calibration trimming of

external circuits.

- Internal system clock derived from RF synthesiser reference oscillator and eliminates the need for additional XTAL or baseband clock oscillator.

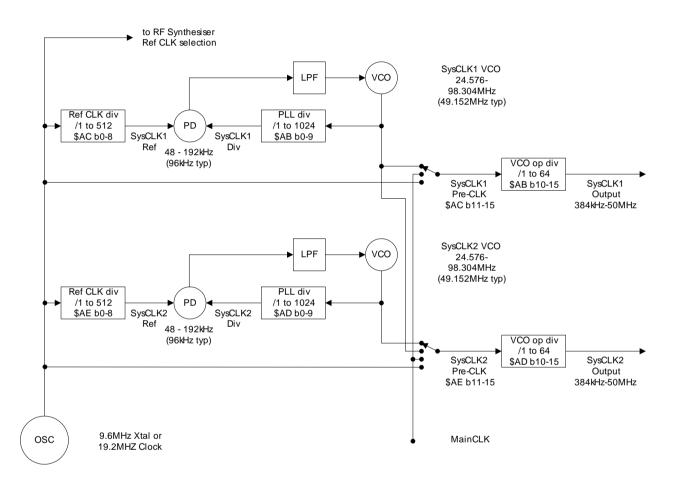

- User clock synthesisers generate two clocks for external use and eliminates an external clock synthesiser when needed to support peripheral devices.

- User selected method for loading a Function Image<sup>™</sup> either from the host µC via C-BUS or from an external serial memory.

- Integrated 2.5V regulator can develop 2.5V from required 3.3V supply.

- Powersave facilities minimize total system power.

# 6.2 AIS system formats

The AIS system uses two basic channel access mechanisms: Self Organising Time Division Multiple Access (SOTDMA) and Carrier-Sensing Time Division Multiple Access (CSTDMA). The CMX7032 and CMX7042 are compatible with both systems and offer additional features which simplify the implementation of CSTDMA. The SOTDMA system is detailed in ITU-R M.1371-1 and IEC 61993-2 while the CSTDMA is detailed in IEC 62287.

The CSTDMA system is used in the implementation of the Class B-CS AIS. This requires the receiver to monitor the first part of a slot for an existing AIS transmission from another station before deciding to use the slot for its own transmission or aborting and selecting a different slot.

The SOTDMA system is used in the Class A and Base Station AIS as well as the Class B-SOTDMA AIS standard.

The CMX7032 and CMX7042 are particularly well suited to the Aids to Navigation applications where power consumption must be minimised.

The relevant International standards are:

| [0] | ITU-R M.1371-4                 |

|-----|--------------------------------|

| [1] | IEC 61993-2 Class A            |

| [2] | IEC 62287-1 Class B CSTDMA     |

| [3] | IEC 62287-2 Class B SOTDMA     |

| [4] | IEC 62320-1 Base Station       |

| [5] | IEC 62320-2 Aids to Navigation |

| [6] | IEC 61097-14AIS-SART           |

# 7 Detailed Descriptions

# 7.1 Clock Source

The CMX7032/CMX7042 can be used with either a 9.6MHz xtal or a 19.2MHz oscillator. The RF clock (RFCLK) should also be derived from this source to avoid the generation of unwanted spurious signals.

# 7.2 Host Interface

This section provides a general description of the C-BUS serial interface protocol used to transfer data, control and status information between the CMX7032/CMX7042 and its host. On the CMX7032 only, the C-BUS serial interface must be enabled by permanently connecting CBUSMODE (pin 57) to digital ground ( $DV_{SS}$ ).

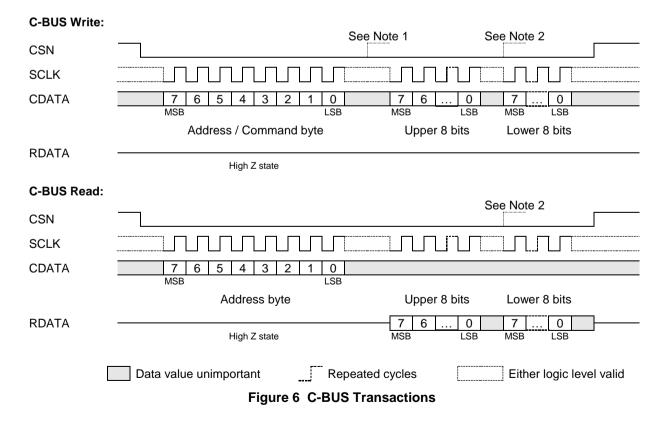

C-BUS is a serial interface, similar to SPI, that uses a simple transaction-oriented command/response protocol with addressing to access specific registers within the CMX7032. Each C-BUS transaction consists of a single Register Address/Command byte (A/C byte) sent from the  $\mu$ C which may be followed by one or more data byte(s) sent from the  $\mu$ C to be written into one of the CMX7032's Write Only registers, or one or more data byte(s) read out from one of the CMX7032's Read Only registers, as illustrated in Figure 6.

Data sent from the  $\mu$ C on the CDATA line is clocked into the CMX7032/CMX7042 on the rising edge of the SCLK input. RDATA sent from the CMX7032/CMX7042 to the  $\mu$ C is valid when the SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine.

The number of data bytes following an A/C byte is dependent on the value of the A/C byte. The most significant bit of the address or data is sent first. For detailed timings see section 8.2.

#### Notes:

- For Command byte transfers only the first 8 bits are transferred.

For single byte data transfers only the first 8 bits of the data are transferred.

The CDATA and RDATA lines are never active at the same time. The Address byte determines the data direction for each C-BUS transfer.

- The SCLK input can be high or low at the start and end of each C-BUS transaction. 4.

- The gaps shown between each byte on the CDATA and RDATA lines in the above diagram are optional, the 5. host may insert gaps or concatenate the data as required.

# 7.3 Function Image<sup>™</sup> Load and Activation

The Function Image<sup>™</sup> (FI) file, which defines the operational capabilities of the device, may be obtained from the CML Technical Portal, following registration. This is in the form of a 'C' header file which can be included into the host controller software or programmed into an external serial memory. The maximum possible size of Function Image<sup>™</sup> is 46kbytes, although a typical FI will be less than this. Note that the BOOTEN pins are only read at power-on or following a C-BUS General Reset and must remain stable throughout the FI loading process. Once the FI load has completed, the BOOTEN pins are ignored by the CMX7032/CMX7042 until the next power-up or C-BUS General Reset.

The BOOTEN pins are both fitted with internal low-current pull down devices.

For C-BUS load operation, both pins should be pulled high by connecting them to  $V_{DD}$  either directly or via a 220k $\Omega$  resistor (see Table 3).

For serial memory load, only BOOTEN1 needs to be pulled high in a similar manner, however, if it is required to program the serial memory in-situ from the host, either a jumper to  $V_{DD}$  or a link to a host I/O pin should be provided to pull BOOTEN2 high when required (see Table 3).

Once the FI has been loaded, the CMX7032/CMX7042 performs these actions:

- (1) the product identification code (\$7032 or \$7042) is reported in C-BUS register \$C5

- (2) the FI version code is reported in C-BUS register \$C9

- (3) the two 32-bit FI checksums are reported in C-BUS register pairs \$A9, \$AA and \$B8, \$B9

- (4) the device waits for the host to load the 32-bit Device Activation Code to C-BUS register \$C8

- (5) once activated, the device initialises fully, enters idle mode and becomes ready for use, and the Activation Register Ready (ACT) flag (bit 0 of the Status register) will be set.

The checksums should be verified against the published values to ensure that the FI has loaded correctly. Once the FI has been activated, the checksum, product identification and version code registers are cleared and these values are no longer available. If an invalid activation code is loaded, the device will report the value \$DEAD in register \$A9 and become unresponsive to all further host commands (including General Reset). A power-on reset is required to recover from this state.

Both the Device Activation Code and the checksum values are available from the CML Technical Portal.

#### Table 3 BOOTEN Pin States

|                    | BOOTEN2 | BOOTEN1 |

|--------------------|---------|---------|

| C-BUS Host load    | 1       | 1       |

| reserved           | 1       | 0       |

| Serial Memory load | 0       | 1       |

| No FI load         | 0       | 0       |

Note: Following a General Reset, reloading of the Function Image is strongly recommended.

#### 7.3.1 FI Loading from Host Controller

The FI can be included into the host controller software build and downloaded into the CMX7032/CMX7042 at power-up over the C-BUS interface. The BOOTEN pins must be set to the C-BUS host load configuration, the CMX7032/CMX7042 powered up, wait for the ACT flag to be set (Status register \$C6 bit 0), then the data can then be sent directly over the C-BUS to the CMX7032/CMX7042.

Each time the device is powered up its Function Image<sup>™</sup> must first be loaded and then activated. These two steps assign internal device resources and determine all device features. The device does not operate until the Function Image<sup>™</sup> is loaded and activated.

#### AIS Baseband IC with/without RF Synthesiser

# Figure 7 FI Loading from Host

The download time is limited by the clock frequency of the C-BUS, with a 5MHz SCLK, it should take less than 500ms to complete.

<sup>© 2018</sup> CML Microsystems Plc

#### 7.3.2 FI Loading from Serial Memory

The FI must be converted into a format for the serial memory programmer (normally Intel Hex) and loaded into the serial memory either by the host or an external programmer. The CMX7032/CMX7042 needs to have the BOOTEN pins set to serial memory load, and then on power-on, or following a C-BUS General Reset, the CMX7032/CMX7042 will automatically load the data from the serial memory without intervention from the host controller.

Figure 8 FI Loading from Serial Memory

The CMX7032/CMX7042 has been designed to function with Atmel AT25HP512 serial EEPROM and the ATF512 flash EEPROM devices<sup>2</sup>, however other manufacturers' parts may also be suitable. The time taken to load the FI is dependent on the XTAL/CLK source frequency, but should be less than 500ms.

<sup>&</sup>lt;sup>2</sup> Note that these two memory devices have slightly different addressing schemes. FI-1.2 for the CMX7032/CMX7042 is compatible with both schemes.

# 7.4 System Description and Tasks

This section describes the operation of main sections of the CMX7032/CMX7042 and the task-oriented logical interface provided to the external host device.

## 7.4.1 Signal Routing

The CMX7032/CMX7042 provides processing capability for two simultaneous receive channels (either two AIS or one AIS and one DSC) or one Tx channel (AIS).

The inputs to the two receiver channels are nominally allocated to the RX1N and RX2N pins of the device, however they can be re-allocated by the user by use of the Input Signal Routing C-BUS register, \$B1. The SpareN pin can also be used as an input to the receivers if required. By default the device will route RX1N to Rx channel 1 and RX2N to Rx channel 2, which leaves the SpareN signal available to the ADC. All of these inputs are configured around an inverting op-amp stage to facilitate gain and filtering adjustments. In addition, the Rx channel inputs are equipped with programmable gain stages for further level adjustments as required.

The Tx Modulation output signals may be configured to be suitable for two-point modulation circuits or alternatively an I/Q upconverter. Signal levels on both output pins, MOD1 and MOD2, can be set to within 0.2dB using a Configuration Mode task.

# 7.4.2 Operating Modes

The CMX7032/CMX7042 operates in either:

- Configuration mode

- Normal mode

Configuration mode is used to set up various operating parameters of the CMX7032/CMX7042 subsystems, e.g. Transmit format, timing parameters etc. following a power-up or reset. The modem section is disabled when the device is in Configuration mode. Configuration mode uses dedicated tasks that are not valid whilst in Normal mode.

Normal mode is used when actively running the CMX7032/CMX7042 modem and other subsystems. Normal mode uses dedicated tasks that are not valid whilst in Configuration mode.

"Enter Config Mode" (ECM) is a Normal mode task that switches the device from Normal to Configuration mode. "Exit Config Mode" (EXIT\_CONFIG) is a Configuration mode task that switches the device from Configuration to Normal mode.

#### 7.4.3 Modem and Data Units

The CMX7032/CMX7042 is logically divided into two main units which can accept and perform tasks separately:

- Modem Unit

- Data Unit

The Modem Unit is primarily responsible for processing Tx data from the internal Tx data buffer, presenting it on the MOD1 and MOD2 pins, processing the Rx input signals to recover the Rx data they represent and storing that data in the internal Rx data buffers.

The Data Unit is primarily responsible for transferring data between the internal data buffers or subsystems and the C-BUS registers, from where they can be accessed by the host  $\mu$ C.

When the device is in Normal mode, the Command register, \$C8, is a 16 bit C-BUS write register that contains task fields for both Data and Modem units. A task is invoked by writing its code into the Data Task or Modem Task fields. A single C-BUS write transaction will change all Command register fields. Often, the host will only want to issue either a Data or Modem task, in which case it should ensure that the other task field is set to all zeroes, corresponding to a null/idle task. Sometimes it is useful to issue Data and Modem tasks simultaneously, in which case, the Data task will always be completed before the Modem task is started.

<sup>© 2018</sup> CML Microsystems Plc

Certain internal subsystems can be directly accessed and controlled via C-BUS transactions, without issuing a specific task/command.

#### 7.4.4 Timing and Synchronisation

An AIS transponder must keep track of both the current AIS slot number and the position within the slot. This is principally to ensure that transmissions occur at the right time, and that hardware is correctly switched between Rx and Tx, but is also useful for scheduling when to take RSSI measurements, when receivers can be powered down and when they should wake up again.

In an AIS Class A transponder, the clock is synchronised with a 1Hz tick from a GNSS (GPS) unit. In a Class B transponder the clock may be synchronised to the GNSS tick, or may be synchronised to the reception time of AIS bursts from a Class A transponder or Base Station. Note that the latter scheme requires management by the host  $\mu$ C, which must determine which received bursts are qualified to be used as a timing reference. Whichever of these methods is used by the transponder, the CMX7032/CMX7042 requires a Slot Clock (SLOTCLK) input from the host  $\mu$ C. This should be a pulse at least 50µs long, whose rising edge is aligned to the AIS Slot boundary. An edge is required at the start of every AIS slot, hence the frequency of this signal is 37.5Hz.

The CMX7032/CMX7042 has several features to assist the host  $\mu$ C with timing, which are detailed below. All of these features are based on the SLOTCLK signal, provided by the host to the CMX7032/CMX7042's SLOTCLK pin. All timings are defined as a number of 24kHz "ticks" referenced to the rising edge of the SLOTCLK signal.

#### 7.4.5 Time of Arrival Reporting

When the CMX7032/CMX7042 has received a burst as the result of an RXB1/2 (receive burst) task, the time of arrival is presented as one of the first four words of the Data Block. This will give the time, measured in 24kHz ticks, between the rising edge of the last SLOTCLK and the detection of the last bit of the start flag of the burst ( $T_{sync}$  in ITU-R M.1371-3). The current Slot Number (as determined by the internal slot counter) will also be returned in the Data Block. Note that the internal filters and signal processing results in a delay of up to 20 ticks – this can be automatically removed by the use of the Config Mode task, ToA compensate. For a received burst from a Class A Transmitter that is exactly aligned with the SLOTCLK, the ToA indicated will be calculated as:

| AIS data field | bits | ticks |

|----------------|------|-------|

| Tx rise time   | 8    | 20    |

| Preamble       | 24   | 60    |

| Start flag     | 8    | 20    |

| Internal delay |      | 20    |

| Total          |      | 120   |

Note that additional delays due to signal processing through external hardware may add to this value.

The internal slot counter increments on every rising edge of the SLOTCLK, or when then the internal tick counter reaches 640. This is not subject to the internal filter delays. The internal tick counter is initialized on every rising edge of SLOTCLK. In the absence of a SLOTCLK signal, it will free-run, based on the internal 24kHz clock, modulo 640. The internal SLOTCLK is output as a pulse on the SLOTCLKOP pin.

# 7.4.6 Tx Timing

The CMX7032/CMX7042 can be configured to perform a sequence of events when a TXB or TDBS task (transmit burst) is issued. The events are: start and end of modulation, ramping the RAMDAC up and down, asserting and releasing a digital output pin (intended as a Tx Enable) and CSTDMA sensing. Each of these can be configured to happen with specified delays from the rising edge of the SLOTCLK. The timings are set up with the Config Mode task Tx\_Sequence. See User Manual section 9.19.2.7 for details.

Figure 9 Tx Burst Timing

If CSTDMA sensing has been enabled then the CMX7032/CMX7042 will measure the carrier level (RSSI) on the selected channel during the window specified in the transmit timing table. If the user-specified threshold is exceeded then the subsequent events (RAMDAC, Tx Enable and modulation) will be cancelled. The threshold is set using the CS\_Threshold register, \$C2. See User Manual section 9.16 for details. The device will output a pulse on the CS-SYNC pin, co-incident with the SLOTCLK, when it intends to attempt a transmission. This is provided to simplify testing under IEC 62287-1 section 12.2.1. The signal will return to its inactive state when the TxDone task is executed, either as a result of a CS abort or if the transmission succeeded.

#### 7.4.7 Rx Timing

The CMX7032/CMX7042 has a powersaving mode, where it spends most of its time 'asleep', but 'wakes up' at the start of each AIS slot and receives for long enough to determine whether a burst is present or not. If no burst is received the CMX7032/CMX7042 will make a pair of RSSI measurements and then go back to sleep. This power saving operation can be turned on and off using the Sleep Mode En bit in the Mode register, \$C1. The CMX7032/CMX7042 will still respond to C-BUS accesses when 'asleep' but the latency between a task being issued and completed may be longer than normal.

The times to perform RSSI measurements, go to sleep, and wake up are configured by the host, and all times are referenced to the SLOTCLK signal. The host should ensure that these timings result in the CMX7032/CMX7042 being awake in time to sample the next SLOTCLK signal. The timings are set up using the Sleep\_Timing Config task. See User Manual section 9.19.2.8 for details.

If Sleep mode is not enabled, then the demodulator will run continuously and update the Rx Data buffer whenever valid data is received.

Figure 10 Rx Burst Timing

# 7.4.8 CSTDMA Threshold Measurement

The CMX7032/CMX7042 provides support for the CSTDMA mode of operation by measuring the signal level at the start of a slot period and aborting the transmission if a level over a user defined threshold is found. This fact is reported to the host in Status2 C-BUS register \$C5.

The CSTDMA threshold measurement window is setup by the Tx\_Sequence Config task using timing values based on the number of 24kHz "tick" increments from the rising edge of the SLOTCLK pulse. During this period (if Tx\_Status and CS-EN are both "active") the CMX7032/CMX7042 will measure the RSSI level of the appropriate channel (set in C-BUS Mode register C1):

- 1. sample RSSI at 48k samples/sec

- 2. scale values to 0 127

- 3. apply the look-up table values

- 4. apply the CSTDMA\_gain value

- 5. accumulate values over the defined period

- 6. compare the value with the value in the C-BUS CS-Threshold register \$C2 and abort the transmission if it is exceeded.

Note that the same lookup table is used for both CSTDMA Threshold measurement as the RSSI measurement.

# 7.4.9 RSSI Measurement

RSSI can not be determined directly from the baseband signal output of a limiter-discriminator device so the CMX7032/CMX7042 has two dedicated inputs (one for each Rx channel) for separate external analogue RSSI signals. Suitable outputs are available on many limiter-discriminator ICs, e.g. Philips SA605. The ADCs sample the signals during a user-defined window and apply an averaging algorithm and present the results in C-BUS registers \$BA and \$BB.

The RSSI measurement windows are set up using the RSSI\_Window config task using timing values based on the number of 24kHz "tick" increments from the rising edge of the SLOTCLK plulse. During this period (if Tx\_Status is not "active") the device will:

- 1. sample RSSI at 48k samples/sec

- 2. scale values to 0 -127

- 3. apply the look-up table values

- 4. apply the RSSI\_gain value

- 5. accumulate values over the defined period

- 6. output values to C-BUS registers

Note that the RSSI measurements on each RF channel run <u>consecutively</u> and that the C-BUS registers are updated at the end of the RSSI\_2 measurement window.

#### 7.4.10 RSSI Calibration