# 16-Bit, 2 MSPS, µModule Data Acquisition Solution

#### **FEATURES**

- Improved design journey

- Fully differential ADC driver with selectable input range

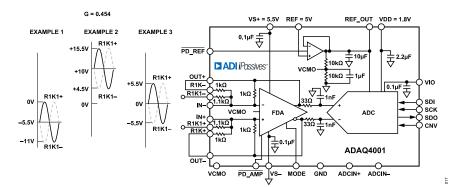

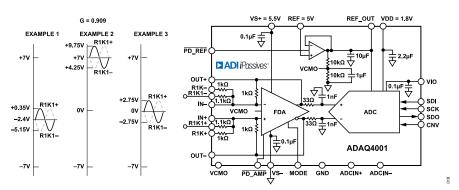

Input ranges with 5 V V<sub>RFF</sub>: ±10 V, ±5 V, or ±2.5 V

- Essential passive components included

- ▶ ±0.005% *i*Passives matched resistor array

- ▶ Wide input common-mode voltage range

- ► High common-mode rejection ratio

- ► Single-ended to differential conversion

- Increased signal chain density

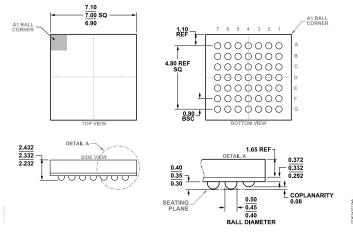

- Small, 7 mm × 7 mm, 0.80 mm pitch, 49-ball CSP\_BGA

- ▶ 4× footprint reduction vs. discrete solution

- ▶ On-board reference buffer with V<sub>CM</sub> generation

- ► High performance

- ► Throughput: 2 MSPS, no pipeline delay

- ▶ Guaranteed 16-bit no missing codes

- ▶ INL: ±4.6 ppm typical, ±11.9 ppm guaranteed

- ▶ SINAD: 95.6 dB typical (G = 0.454)

- ▶ Offset error drift: 0.7 ppm/°C typical (G = 0.454)

- ▶ Gain error drift: ±0.5 ppm/°C typical

- ▶ Low total power dissipation: 51.6 mW typical at 2 MSPS

- ▶ SPI-/QSPI<sup>™</sup>-/MICROWIRE<sup>™</sup>-/DSP-compatible serial interface

- ▶ Versatile logic interface supply with 1.8 V, 2.5 V, 3 V, or 5 V

### **APPLICATIONS**

- Automatic test equipment

- Machine automation

- Process controls

- Medical instrumentation

- Digital control loops

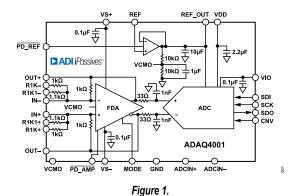

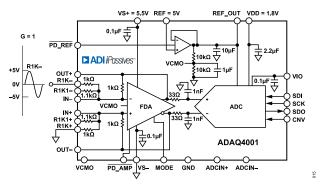

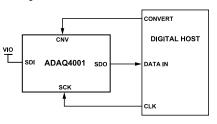

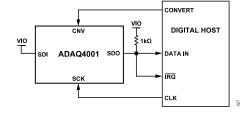

### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

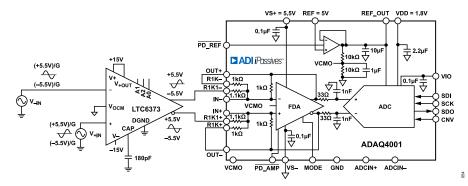

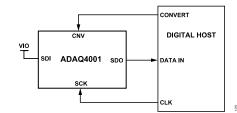

The ADAQ4001 is a  $\mu$ Module<sup>®</sup> precision data acquisition (DAQ), signal chain solution that reduces the development cycle of a precision measurement system by transferring the signal chain design challenge of component selection, optimization, and layout from the designer to the device.

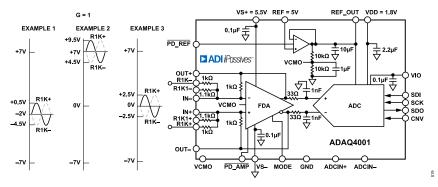

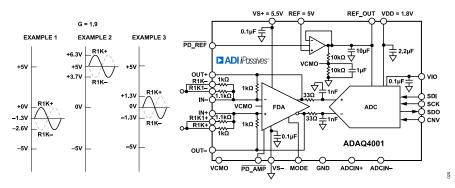

Using system-in-package (SIP) technology, the ADAQ4001 reduces end system component count by combining multiple common signal processing and conditioning blocks into a single device. These blocks include a high resolution 16-bit, 2 MSPS successive approximation register (SAR), analog-to-digital converter (ADC), a low noise, fully differential ADC driver amplifier (FDA), and a stable reference buffer.

Using Analog Devices, Inc., *i*Passives<sup>®</sup> technology, the ADAQ4001 also incorporates crucial passive components with superior matching and drift characteristics to minimize temperature dependent error sources and to offer optimized performance (see Figure 1). Housing this signal chain solution in a small, 7 mm × 7 mm, 0.80 mm pitch, 49-ball chip scale package ball grid array (CSP\_BGA) enables compact form factor designs without sacrificing performance and simplifies end system bill of materials management. This level of system integration makes the ADAQ4001 much less sensitive to printed circuit board (PCB) layout while still providing flexibility to adapt to a wide range of signal levels.

The serial peripheral interface (SPI)-compatible, serial user interface is compatible with 1.8 V, 2.5 V, 3 V, or 5 V logic, using a separate VIO supply. The specified operation of theADAQ4001 is from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### Table 1. µModule Data Acquisition Solutions

| Туре   | 500 kSPS | ≥1000 kSPS         |

|--------|----------|--------------------|

| 16-Bit | ADAQ7988 | ADAQ7980, ADAQ4001 |

| 18-bit |          | ADAQ4003           |

Rev. A

DOCUMENT FEEDBACK

**TECHNICAL SUPPORT**

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| General Description                         | 1  |

| Specifications                              | 3  |

| Timing Specifications                       | 7  |

| Absolute Maximum Ratings                    | 9  |

| Thermal Resistance                          | 9  |

| Electrostatic Discharge (ESD) Ratings       | 9  |

| ESD Caution                                 | 9  |

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 12 |

| Terminology                                 |    |

| Theory of Operation                         | 20 |

| Circuit Information                         | 20 |

| Transfer Functions                          | 20 |

| Applications Information                    | 21 |

| Typical Application Diagrams                |    |

| Analog Inputs                               | 24 |

| Ease of Drive Features                    | 24   |

|-------------------------------------------|------|

| Voltage Reference Input                   | 26   |

| Power Supply (Power Tree)                 |      |

| Power-Down Mode                           |      |

| Digital Interface                         | . 26 |

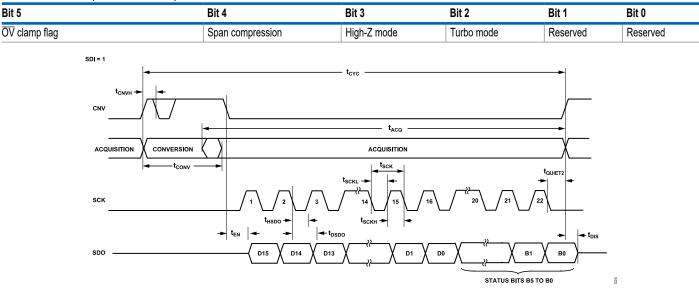

| Register Read and Write Functionality     | 27   |

| Status Word                               | 29   |

| 3-Wire CS Turbo Mode                      | . 30 |

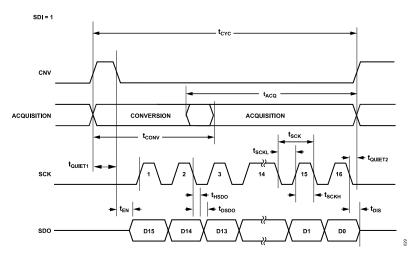

| 3-Wire CS Mode Without the Busy Indicator |      |

| 3-Wire CS Mode with the Busy Indicator    | 32   |

| 4-Wire CS Turbo Mode                      | . 33 |

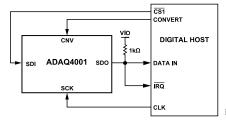

| 4-Wire CS Mode Without the Busy Indicator | 34   |

| 4-Wire CS Mode with the Busy Indicator    | 35   |

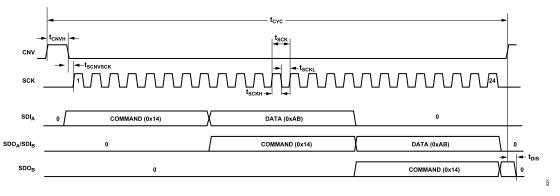

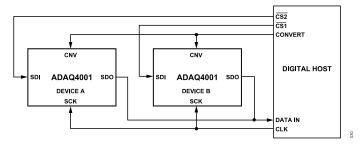

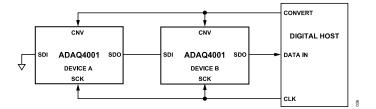

| Daisy-Chain Mode                          | 36   |

| Layout Guidelines                         | 37   |

| Outline Dimensions                        | . 38 |

| Ordering Guide                            | 38   |

| Evaluation Boards                         | 38   |

# **REVISION HISTORY**

#### 2/2022—Rev. 0 to Rev. A

| Changes to Transition Noise Parameter, Table 2        | 3  |

|-------------------------------------------------------|----|

| Changes to Thermal Resistance Section and Table 7     |    |

| Changes to Figure 5, Figure 6, Figure 8, and Figure 9 | 12 |

| Changes to Figure 28                                  | 15 |

| Changes to Figure 38                                  | 17 |

| Changes to Power-Down Mode Section                    |    |

| -                                                     |    |

#### 5/2021—Revision 0: Initial Version

VDD = 1.8 V ± 5%, VS+ = 5.5 V ± 5%, VS- = 0 V, VIO = 1.7 V to 5.5 V, reference voltage ( $V_{REF}$ ) = 5 V, sampling frequency ( $f_S$ ) = 2 MSPS, all specifications  $T_{MIN}$  to  $T_{MAX}$ , high-Z mode disabled, span compression disabled, and turbo mode enabled, unless otherwise noted. ADC driver configured in single-ended to differential configuration and normal mode, unless otherwise noted.

| Parameter                                                                 | Test Conditions/Comments                                            | Min                       | Тур    | Max                       | Unit             |

|---------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------|--------|---------------------------|------------------|

| RESOLUTION                                                                |                                                                     | 16                        |        |                           | Bit              |

| ANALOG INPUTS                                                             | IN+, IN-, R1K1+, R1K1-, R1K+, and R1K-                              |                           |        |                           |                  |

| Input Impedance (Z <sub>IN</sub> )                                        | Single-ended to differential configuration                          |                           |        |                           |                  |

|                                                                           | G = 0.454, input voltage (V <sub>IN</sub> ) = 22 V p-p              |                           | 1.3    |                           | kΩ               |

|                                                                           | G = 0.909, V <sub>IN</sub> = 11 V p-p                               |                           | 1.44   |                           | kΩ               |

|                                                                           | G = 1, V <sub>IN</sub> = 10 V p-p                                   |                           | 1.33   |                           | kΩ               |

|                                                                           | G = 1.9, V <sub>IN</sub> = 5.2 V p-p                                |                           | 778    |                           | Ω                |

|                                                                           | Fully differential configuration                                    |                           |        |                           |                  |

|                                                                           | G = 0.454 and G = 0.909, V <sub>IN</sub> = 22 V p-p and<br>11 V p-p |                           | 1.1    |                           | kΩ               |

|                                                                           | G = 1, V <sub>IN</sub> = 10 V p-p                                   |                           | 1      |                           | kΩ               |

|                                                                           | G = 1.9, V <sub>IN</sub> = 5.2 V p-p                                |                           | 523    |                           | Ω                |

| Differential Input Voltage Ranges <sup>1</sup>                            | G = 0.454, V <sub>IN</sub> = 22 V p-p                               | -2.2 × V <sub>REF</sub>   |        | +2.2 × V <sub>REF</sub>   | V                |

|                                                                           | G = 0.909, V <sub>IN</sub> = 11 V p-p                               | -1.1 × V <sub>RFF</sub>   |        | +1.1 × V <sub>REF</sub>   | V                |

|                                                                           | G = 1, V <sub>IN</sub> = 10 V p-p                                   | -V <sub>REF</sub>         |        | +V <sub>REF</sub>         | V                |

|                                                                           | $G = 1.9, V_{IN} = 5.2 V p-p$                                       | -0.526 × V <sub>REF</sub> |        | +0.526 × V <sub>REF</sub> | V                |

| Input Capacitance                                                         | IN+ and IN-                                                         |                           | 15     |                           | pF               |

| THROUGHPUT                                                                |                                                                     |                           |        |                           |                  |

| Complete Cycle                                                            |                                                                     | 500                       |        |                           | ns               |

| Conversion Time                                                           |                                                                     |                           | 290    | 320                       | ns               |

| Acquisition Phase <sup>2</sup>                                            |                                                                     | 290                       |        |                           | ns               |

| Throughput Rate <sup>3</sup>                                              |                                                                     | 0                         |        | 2                         | MSPS             |

| Transient Response <sup>4</sup>                                           |                                                                     |                           | 40     |                           | μs               |

| DC ACCURACY                                                               | Single-ended to differential configuration                          |                           |        |                           |                  |

| No Missing Codes                                                          |                                                                     | 16                        |        |                           | Bits             |

| Integral Nonlinearity Error (INL)                                         | All gains, VS− = −1 V                                               | -11.9                     | ±4.6   | +11.9                     | ppm              |

|                                                                           |                                                                     | -0.78                     | ±0.3   | +0.78                     | LSB <sup>5</sup> |

| Differential Nonlinearity Error (DNL)                                     | All gains, VS− = −1 V                                               | -9.56                     | ±3.8   | +9.56                     | ppm              |

|                                                                           |                                                                     | -0.63                     | ±0.25  | +0.63                     | LSB <sup>5</sup> |

| Transition Noise                                                          | G = 0.454                                                           |                           | 0.37   |                           | LSB              |

|                                                                           | G = 0.909                                                           |                           | 0.41   |                           | LSB              |

|                                                                           | G = 1                                                               |                           | 0.4    |                           | LSB              |

|                                                                           | G = 1.9                                                             |                           | 0.4    |                           | LSB              |

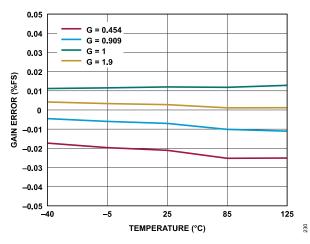

| Gain Error                                                                | All gains                                                           | -0.05                     | ±0.005 | +0.05                     | % FS             |

| Gain Error Drift                                                          | All gains                                                           | -3                        | ±0.5   | +3                        | ppm/°C           |

| Offset Error                                                              | G = 0.454                                                           | -1                        | ±0.1   | +1                        | mV               |

|                                                                           | G = 0.909, G = 1                                                    | -0.9                      | ±0.06  | +0.9                      | mV               |

|                                                                           | G = 1.9                                                             | -1.5                      | ±0.01  | +1.5                      | mV               |

| Offset Error Drift                                                        | G = 0.454                                                           | -8                        | +0.7   | +8                        | ppm/°C           |

|                                                                           | G = 0.909 and G = 1                                                 | -10                       | +1.6   | +10                       | ppm/°C           |

|                                                                           | G = 1.9                                                             | -15                       | +2.6   | +15                       | ppm/°C           |

| Common-Mode Rejection Ratio (CMRR)<br>Power Supply Rejection Ratio (PSRR) | Fully differential configuration, all gains                         |                           | 90     |                           | dB               |

| Positive                                                                  | VDD = 1.71 V to 1.89 V                                              |                           | 72     |                           | dB               |

|                                                                           | VS+ = 5.225 V to 5.775 V, VS- = 0 V                                 |                           | 110    |                           | dB               |

Table 2.

| Parameter                                  | Test Conditions/Comments                                                                       | Min  | Тур Мах   | Unit   |

|--------------------------------------------|------------------------------------------------------------------------------------------------|------|-----------|--------|

| Negative                                   | VS+ = +5.5 V, VS- = 0 V to -0.5 V                                                              |      | 107       | dB     |

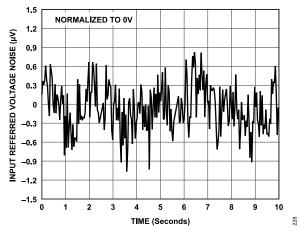

| 1/f Noise <sup>6</sup>                     | Referred to input, bandwidth = 0.1 Hz to 10 Hz,<br>normalized to 0 V, all gains                | 2    |           | µV р-р |

| Input Current Noise                        | Input frequency (f <sub>IN</sub> ) = 100 kHz                                                   |      | 1         | pA/√Hz |

| AC ACCURACY                                | Single-ended to differential and fully differential configuration                              |      |           |        |

| Dynamic Range                              | All gains, -60 dBFS                                                                            | 93.0 |           | dB     |

|                                            | G = 0.454                                                                                      |      | 95.8      | dB     |

|                                            | G = 0.909                                                                                      |      | 95        | dB     |

|                                            | G = 1                                                                                          |      | 95.3      | dB     |

|                                            | G = 1.9                                                                                        |      | 95.2      | dB     |

| Oversampled Dynamic Range                  | Oversampling ratio (OSR) = 2, all gains                                                        |      | 99        | dB     |

|                                            | OSR = 256, all gains                                                                           |      | 118       | dB     |

| Total RMS Noise (Referred to Output (RTO)) | G = 0.454                                                                                      |      | 57        | μV rms |

|                                            | G = 0.909                                                                                      |      | 63.2      | μV rms |

|                                            | G = 1                                                                                          |      | 60.9      | μV rms |

|                                            | G = 1.9                                                                                        |      | 61.3      | μV rms |

| Noise Spectral Density <sup>7</sup>        | G = 0.454                                                                                      |      | 21.7      | nV/√Hz |

|                                            | G = 0.909                                                                                      |      | 24        | nV/√Hz |

|                                            | G = 1                                                                                          |      | 23.2      | nV/√Hz |

|                                            | G = 1.9                                                                                        |      | 23.3      | nV/√Hz |

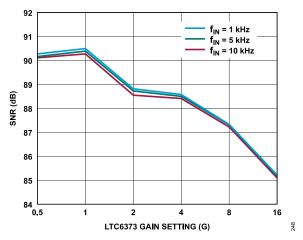

| Signal-to-Noise Ratio (SNR)                | f <sub>IN</sub> = 1 kHz, −0.5 dBFS                                                             | 92.7 |           | dB     |

| 5                                          | G = 0.454                                                                                      |      | 95.6      | dB     |

|                                            | G = 0.909                                                                                      |      | 94.3      | dB     |

|                                            | G = 1                                                                                          |      | 95.3      | dB     |

|                                            | G = 1.9                                                                                        |      | 94.9      | dB     |

|                                            | f <sub>IN</sub> = 100 kHz, G = 0.909                                                           |      | 94.3      | dB     |

|                                            | $f_{IN} = 400 \text{ kHz}, G = 0.909$                                                          |      | 87.7      | dB     |

|                                            | Low power mode enabled, $G = 0.909$                                                            |      | 94.5      | dB     |

|                                            | $VS$ = 3.3 V, $VS$ = 0 V, $V_{REF}$ = 2.5 V, G = 0.909                                         |      | 91.5      | dB     |

| Signal-to-Noise + Distortion (SINAD)       | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}$                                                    | 92.5 | 01.0      | dB     |

|                                            | G = 0.454                                                                                      | 02.0 | 95.6      | dB     |

|                                            | G = 0.909                                                                                      |      | 94.2      | dB     |

|                                            | G = 1                                                                                          |      | 95.3      | dB     |

|                                            | G = 1.9                                                                                        |      | 94.8      | dB     |

|                                            | f <sub>IN</sub> = 100 kHz, G = 0.909                                                           |      | 93.8      | dB     |

|                                            | $f_{\rm IN} = 400 \text{ kHz}, \text{ G} = 0.909$                                              |      | 85.6      | dB     |

|                                            | Low power mode enabled, $G = 0.909$                                                            |      | 94.4      | dB     |

|                                            | $VS$ = 3.3 V, $VS$ = 0 V, $V_{REF}$ = 2.5 V, G = 0.909                                         |      | 91.4      | dB     |

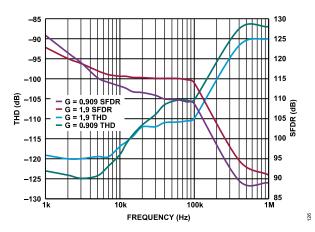

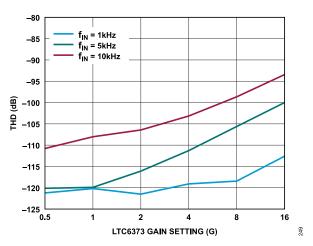

| Total Harmonic Distortion (THD)            | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}, \text{ all gains}$                                 |      | -120      | dB     |

|                                            | $f_{\rm IN} = 100 \rm kHz, G = 0.909$                                                          |      | -100      | dB     |

|                                            | $f_{\rm IN} = 400 \text{ kHz}, \text{ G} = 0.909$                                              |      | -95       | dB     |

|                                            | Low power mode enabled, $G = 0.909$                                                            |      | -110      | dB     |

|                                            | $VS + = 3.3 V, VS - = 0 V, V_{REF} = 2.5 V, G = 0.909$                                         |      | -118      | dB     |

| Spurious-Free Dynamic Range (SFDR)         | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}, \text{ all gains}$                                 |      | 122       | dB     |

| opunous-i ree dynamic range (SEDR)         | $f_{IN} = 100 \text{ kHz}, -0.5 \text{ dBr-S}, an gains f_{IN} = 100 \text{ kHz}, G = 0.909$   |      | 101       | dB     |

|                                            | $f_{IN} = 400 \text{ kHz}, \text{ G} = 0.909$<br>$f_{IN} = 400 \text{ kHz}, \text{ G} = 0.909$ |      | 95        | dB     |

|                                            | $I_{IN} = 400$ kHz, G = 0.909<br>Low power mode enabled, G = 0.909                             |      | 95<br>110 | dB     |

|                                            | $VS+ = 3.3 V, VS- = 0 V, V_{REF} = 2.5 V, G = 0.909$                                           |      | 118       | dB     |

### Table 2.

| Parameter                                      | Test Conditions/Comments                        | Min                         | Тур                 | Max                         | Unit   |

|------------------------------------------------|-------------------------------------------------|-----------------------------|---------------------|-----------------------------|--------|

| −3 dB Input Bandwidth                          |                                                 |                             | 4.4                 |                             | MHz    |

| Aperture Delay                                 |                                                 |                             | 1                   |                             | ns     |

| Aperture Jitter                                |                                                 |                             | 1                   |                             | ps rms |

| REFERENCE                                      |                                                 |                             |                     |                             |        |

| V <sub>REF</sub> Range                         | Buffer enabled                                  | 2.4                         |                     | 5.1 or VS+ - 0.08           | V      |

| Input Current (I <sub>REF</sub> )              | Buffer enabled                                  |                             | 60                  |                             | μA     |

| REF_OUT Current (I <sub>REF_OUT</sub> )        | Buffer disabled, 2 MSPS, V <sub>RFF</sub> = 5 V |                             | 1.27                |                             | mA     |

| /CMO                                           |                                                 |                             |                     |                             |        |

| VCMO Voltage (V <sub>VCMO</sub> ) <sup>8</sup> |                                                 | V <sub>REF</sub> /2 - 0.003 | V <sub>REF</sub> /2 | V <sub>REF</sub> /2 + 0.003 | V      |

| Output Impedance                               |                                                 |                             | 5                   |                             | kΩ     |

| DIGITAL INPUTS                                 | SDI, SCK, and CNV                               |                             |                     |                             |        |

| Logic Levels                                   |                                                 |                             |                     |                             |        |

| Input Low Voltage (VIL)                        | VIO > 2.7 V                                     | -0.3                        |                     | +0.3 × VIO                  | V      |

|                                                | VIO ≤ 2.7 V                                     | -0.3                        |                     | +0.2 × VIO                  | V      |

| Input High Voltage (V)                         | VIO = 2.7 V<br>VIO > 2.7 V                      | -0.3<br>0.7 × VIO           |                     | VIO + 0.3                   |        |

| Input High Voltage (V <sub>IH</sub> )          | $VIO \ge 2.7 V$ $VIO \le 2.7 V$                 | 0.7 × VIO<br>0.8 × VIO      |                     |                             | V<br>V |

| Input Low Current (L)                          | $VIU \ge 2.1 V$                                 |                             |                     | VIO + 0.3                   |        |

| Input Low Current (I <sub>L</sub> )            |                                                 | -1                          |                     | +1                          | μA     |

| Input High Current (I <sub>IH</sub> )          |                                                 | -1                          | 0                   | +1                          | μA     |

| Input Pin Capacitance                          |                                                 |                             | 6                   |                             | pF     |

| DIGITAL OUTPUTS <sup>9</sup>                   |                                                 |                             | _                   |                             |        |

| Data Format                                    |                                                 |                             | Twos comp           |                             |        |

| Output Low Voltage (V <sub>OL</sub> )          | Sink current (I <sub>SINK</sub> ) = +500 µA     |                             |                     | 0.4                         | V      |

| Output High Voltage (V <sub>OH</sub> )         | Source current (I <sub>SOURCE</sub> ) = −500 µA | VIO - 0.3                   |                     |                             | V      |

| POWER-DOWN MODE                                |                                                 |                             |                     |                             |        |

| FDA and Reference Buffer                       |                                                 |                             |                     |                             |        |

| PD_REF, PD_AMP                                 |                                                 |                             |                     |                             |        |

| Low                                            | Powered down, low power mode                    |                             | <1                  |                             | V      |

| High                                           | Enabled, normal mode                            |                             | >1.7                |                             | V      |

| Turn-On Time                                   | All devices enabled                             |                             |                     |                             |        |

|                                                | Low to high <sup>10</sup>                       |                             | 120                 |                             | μs     |

|                                                | High <sup>11</sup>                              |                             | 1                   |                             | μs     |

| POWER REQUIREMENTS                             |                                                 |                             |                     |                             |        |

| VDD                                            |                                                 | 1.71                        | 1.8                 | 1.89                        | V      |

| VS+                                            |                                                 | 3                           | 5.5                 | VS- + 10                    | V      |

| VS-                                            |                                                 | VS+ - 10                    | 0                   | 0.1                         | V      |

| VIO                                            |                                                 | 1.7                         | -                   | 5.5                         | V      |

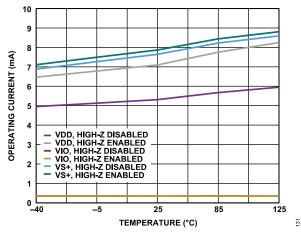

| Total Standby Current <sup>12, 13</sup>        | Static, all devices enabled                     |                             |                     |                             |        |

|                                                | Normal mode                                     |                             | 11                  | 14                          | mA     |

|                                                | Low power mode                                  |                             | 6.5                 | 8.3                         | mA     |

| Power-Down Current                             | ADC driver, reference buffer disabled           |                             | 100                 | 250                         | μΑ     |

| Power Dissipation                              | VDD = VIO = 1.8 V, VS + = 5.5 V, VS - = 0 V     |                             | 100                 | 200                         | µ/٦    |

| Normal Mode                                    |                                                 |                             |                     |                             |        |

| VS+                                            |                                                 |                             | 41.5                | 51 F                        | m\//   |

|                                                |                                                 |                             |                     | 51.5                        | mW     |

| VDD                                            |                                                 |                             | 9.5                 | 12.0                        | mW     |

| VIO                                            |                                                 |                             | 0.6                 | 0.7                         | mW     |

| Total                                          |                                                 |                             | 51.6                | 64.2                        | mW     |

|                                                | High-Z mode enabled                             |                             |                     |                             |        |

| VS+                                            |                                                 |                             | 44.0                | 53.0                        | mW     |

#### Table 2.

| Parameter             | Test Conditions/Comments             | Min | Тур  | Max  | Unit |

|-----------------------|--------------------------------------|-----|------|------|------|

| VDD                   |                                      |     | 12.8 | 16.5 | mW   |

| VIO                   |                                      |     | 0.6  | 0.7  | mW   |

| Total                 |                                      |     | 57.4 | 70.2 | mW   |

| Low Power Mode        |                                      |     |      |      |      |

| VS+                   |                                      |     | 30.2 | 37.4 | mW   |

| VDD                   |                                      |     | 9.5  | 12.0 | mW   |

| VIO                   |                                      |     | 0.5  | 0.6  | mW   |

| Total                 |                                      |     | 40.2 | 50.0 | mW   |

|                       | High-Z mode enabled                  |     |      |      |      |

| VS+                   |                                      |     | 31.4 | 37.8 | mW   |

| VDD                   |                                      |     | 12.7 | 16.4 | mW   |

| VIO                   |                                      |     | 0.5  | 0.6  | mW   |

| Total                 |                                      |     | 44.6 | 54.8 | mW   |

| EMPERATURE RANGE      |                                      |     |      |      |      |

| Specified Performance | T <sub>MIN</sub> to T <sub>MAX</sub> | -40 |      | +125 | °C   |

<sup>1</sup> V<sub>IN</sub> must be within the allowed input common-mode range as per Figure 35, Figure 36, and Figure 37 and is dependent on the VS+ and VS- supply rails used.

<sup>2</sup> The acquisition phase is the time available for the input sampling capacitors to acquire a new input with the ADC running at a throughput rate of 2 MSPS.

<sup>3</sup> A throughput rate of 2 MSPS can only be achieved with turbo mode enabled and a minimum SCK rate of 70 MHz. Refer to Table 5 for the maximum achievable throughput for different modes of operation.

<sup>4</sup> Transient response is the time required for the ADAQ4001 to acquire a full-scale input step to ±1 LSB accuracy.

<sup>5</sup> The weight of the LSB, referred to input, changes depending on the input voltage range. See Table 10 for the LSB size.

<sup>6</sup> See the 1/f noise plot in Figure 28.

<sup>7</sup> Noise Spectral Density for each gain can be calculated using the equation: Total RMS Noise (RTO)/ $\sqrt{(\pi/2 \times bandwidth)}$ , where bandwidth is the -3 dB Input Bandwidth equal to 4.4 MHz.

<sup>8</sup> The VCMO voltage can be used for other circuitry, but it should be driven with a buffer to ensure the VCMO voltage remains stable as per the specified range.

<sup>9</sup> There is no pipeline delay. Conversion results are available immediately after a conversion is completed.

<sup>10</sup> The time it takes for a reference buffer to charge a 10 µF reference capacitor to 90% of the reference voltage.

<sup>11</sup> The time it takes for the FDA to charge the 1 nF filter capacitor to 90% of the final value.

<sup>12</sup> With all digital inputs forced to VIO or GND as required.

<sup>13</sup> The total standby current during the acquisition phase.

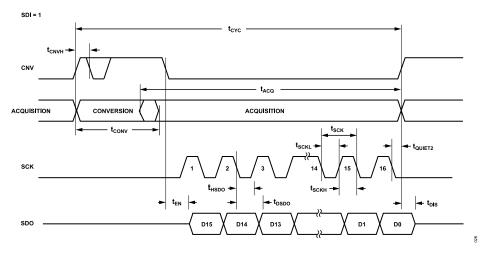

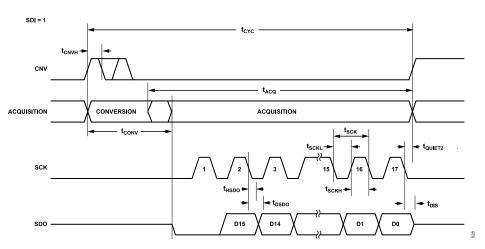

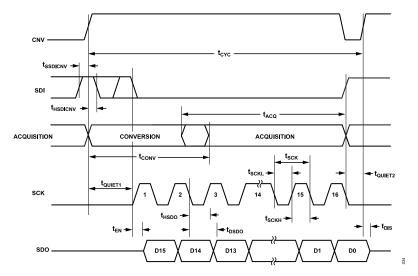

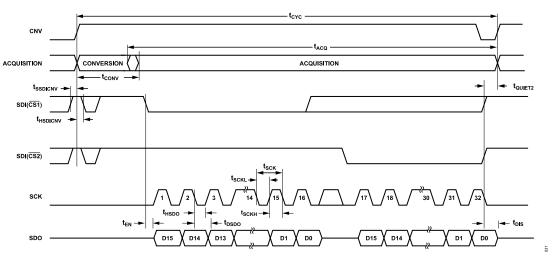

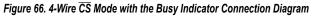

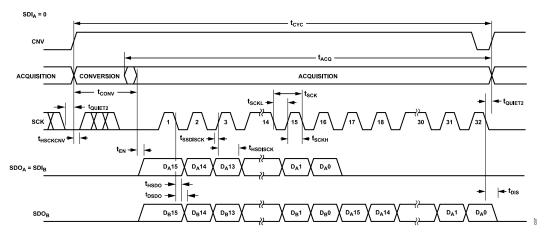

# TIMING SPECIFICATIONS

VDD = 1.8 V ± 5%, VS+ = 5.5 V ± 5%, VS- = 0 V, VIO = 1.71 V to 5.5V,  $V_{REF}$  = 5 V,  $f_S$  = 2 MSPS, all specifications  $T_{MIN}$  to  $T_{MAX}$ , high-Z mode disabled, span compression disabled, and turbo mode enabled, unless otherwise noted.

#### Table 3. Digital Interface Timing

| Parameter                                                                | Symbol               | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------|----------------------|------|-----|------|------|

| Conversion Time—CNV Rising Edge to Data Available                        | t <sub>CONV</sub>    |      | 290 | 320  | ns   |

| Acquisition Phase <sup>1</sup>                                           | t <sub>ACQ</sub>     | 290  |     |      | ns   |

| Time Between Conversions                                                 | t <sub>CYC</sub>     | 500  |     |      | ns   |

| CNV Pulse Width (CS Mode) <sup>2</sup>                                   | t <sub>CNVH</sub>    | 10   |     |      | ns   |

| SCK Period (CS Mode) <sup>3</sup>                                        | t <sub>SCK</sub>     |      |     |      |      |

| VIO > 2.7 V                                                              |                      | 9.8  |     |      | ns   |

| VIO > 1.7 V                                                              |                      | 12.3 |     |      | ns   |

| SCK Period (Daisy-Chain Mode) <sup>4</sup>                               | t <sub>SCK</sub>     |      |     |      |      |

| VIO > 2.7 V                                                              |                      | 20   |     |      | ns   |

| VIO > 1.7 V                                                              |                      | 25   |     |      | ns   |

| SCK Low Time                                                             | t <sub>SCKL</sub>    | 3    |     |      | ns   |

| SCK High Time                                                            | t <sub>scкн</sub>    | 3    |     |      | ns   |

| SCK Falling Edge to Data Remains Valid Delay                             | t <sub>HSDO</sub>    | 1.5  |     |      | ns   |

| SCK Falling Edge to Data Valid Delay                                     | t <sub>DSDO</sub>    |      |     |      |      |

| VIO > 2.7 V                                                              |                      |      |     | 7.5  | ns   |

| VIO > 1.7 V                                                              |                      |      |     | 10.5 | ns   |

| CNV or SDI Low to SDO D15 MSB Valid Delay (CS Mode)                      | t <sub>EN</sub>      |      |     |      |      |

| VIO > 2.7 V                                                              |                      |      |     | 10   | ns   |

| VIO > 1.7 V                                                              |                      |      |     | 13   | ns   |

| CNV Rising Edge to First SCK Rising Edge Delay                           | t <sub>QUIET1</sub>  | 190  |     |      | ns   |

| Last SCK Falling Edge to CNV Rising Edge Delay                           | t <sub>QUIET2</sub>  | 60   |     |      | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) | t <sub>DIS</sub>     |      |     | 20   | ns   |

| SDI Valid Setup Time from CNV Rising Edge                                | t <sub>SSDICNV</sub> | 2    |     |      | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                       | t <sub>HSDICNV</sub> | 2    |     |      | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Daisy-Chain Mode)              | t <sub>HSCKCNV</sub> | 12   |     |      | ns   |

| SDI Valid Setup Time from SCK Rising Edge (Daisy-Chain Mode)             | t <sub>SSDISCK</sub> | 2    |     |      | ns   |

| SDI Valid Hold Time from SCK Rising Edge (Daisy-Chain Mode)              | t <sub>HSDISCK</sub> | 2    |     |      | ns   |

<sup>1</sup> The acquisition phase is the time available for the input sampling capacitors to acquire a new input with the ADC running at a throughput rate of 2 MSPS.

$^2~$  For turbo mode,  $t_{\mbox{CNVH}}$  must match the  $t_{\mbox{QUIET1}}$  minimum.

<sup>3</sup> A throughput rate of 2 MSPS can only be achieved with turbo mode enabled and a minimum SCK rate of 70 MHz.

<sup>4</sup> A 50% duty cycle is assumed for SCK.

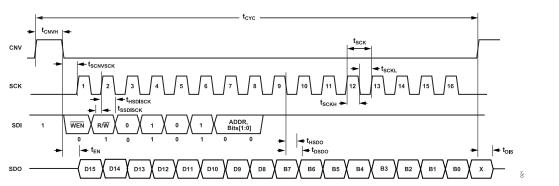

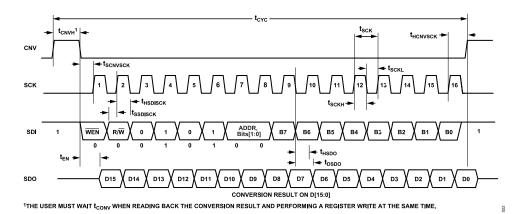

#### Table 4. Register Read and Write Timing

| Parameter                                      | Symbol               | Min  | Тур | Max  | Unit |

|------------------------------------------------|----------------------|------|-----|------|------|

| READ AND WRITE OPERATION                       |                      |      |     |      |      |

| CNV Pulse Width <sup>1</sup>                   | t <sub>CNVH</sub>    | 10   |     |      | ns   |

| SCK Period                                     | t <sub>SCK</sub>     |      |     |      |      |

| VIO > 2.7 V                                    |                      | 9.8  |     |      | ns   |

| VIO > 1.7 V                                    |                      | 12.3 |     |      | ns   |

| SCK Low Time                                   | t <sub>SCKL</sub>    | 3    |     |      | ns   |

| SCK High Time                                  | t <sub>scкн</sub>    | 3    |     |      | ns   |

| READ OPERATION                                 |                      |      |     |      |      |

| CNV Low to SDO D15 MSB Valid Delay             | t <sub>EN</sub>      |      |     |      |      |

| VIO > 2.7 V                                    |                      |      |     | 10   | ns   |

| VIO > 1.7 V                                    |                      |      |     | 13   | ns   |

| SCK Falling Edge to Data Remains Valid         | t <sub>HSDO</sub>    | 1.5  |     |      | ns   |

| SCK Falling Edge to Data Valid Delay           | t <sub>DSDO</sub>    |      |     |      |      |

| VIO > 2.7 V                                    |                      |      |     | 7.5  | ns   |

| VIO > 1.7 V                                    |                      |      |     | 10.5 | ns   |

| CNV Rising Edge to SDO High Impedance          | t <sub>DIS</sub>     |      |     | 20   | ns   |

| WRITE OPERATION                                |                      |      |     |      |      |

| SDI Valid Setup Time from SCK Rising Edge      | tssdisck             | 2    |     |      | ns   |

| SDI Valid Hold Time from SCK Rising Edge       | t <sub>HSDISCK</sub> | 2    |     |      | ns   |

| CNV Rising Edge to SCK Edge Hold Time          | t <sub>HCNVSCK</sub> | 0    |     |      | ns   |

| CNV Falling Edge to SCK Active Edge Setup Time | t <sub>SCNVSCK</sub> | 6    |     |      | ns   |

$^1~$  For turbo mode,  $t_{\text{CNVH}}$  must match the  $t_{\text{QUIET1}}$  minimum.

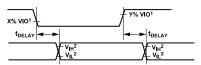

1FOR VIO  $\leq$  2.7V, X = 80, AND Y = 20; FOR VIO > 2.7V, X = 70, AND Y = 30. 2MINIMUM VIH AND MAXIMUM VIL USED. SEE DIGITAL INPUTS SPECIFICATIONS IN TABLE 2.

#### Figure 2. Voltage Levels for Timing

#### Table 5. Achievable Throughput for Different Modes of Operation

| Parameter                                        | Test Conditions/Comments                                 | Min | Тур | Max  | Unit |

|--------------------------------------------------|----------------------------------------------------------|-----|-----|------|------|

| THROUGHPUT, CS MODE                              |                                                          |     |     |      |      |

| 3-Wire and 4-Wire Turbo Mode                     | SCK frequency (f <sub>SCK</sub> ) = 100 MHz, VIO ≥ 2.7 V |     |     | 2    | MSPS |

|                                                  | f <sub>SCK</sub> = 80 MHz, VIO < 2.7 V                   |     |     | 2    | MSPS |

| 3-Wire and 4-Wire Turbo Mode and Six Status Bits | f <sub>SCK</sub> = 100 MHz, VIO ≥ 2.7 V                  |     |     | 2    | MSPS |

|                                                  | f <sub>SCK</sub> = 80 MHz, VIO < 2.7 V                   |     |     | 1.86 | MSPS |

| 3-Wire and 4-Wire Mode                           | f <sub>SCK</sub> = 100 MHz, VIO ≥ 2.7 V                  |     |     | 1.82 | MSPS |

|                                                  | f <sub>SCK</sub> = 80 MHz, VIO < 2.7 V                   |     |     | 1.69 | MSPS |

| 3-Wire and 4-Wire Mode and Six Status Bits       | f <sub>SCK</sub> = 100 MHz, VIO ≥ 2.7 V                  |     |     | 1.64 | MSPS |

|                                                  | f <sub>SCK</sub> = 80 MHz, VIO < 2.7 V                   |     |     | 1.5  | MSPS |

#### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                      | Rating                                 |

|--------------------------------|----------------------------------------|

| Analog Inputs                  |                                        |

| R1K+, R1K-,R1K1+, R1K1- to GND | -16 V to +16 V or ±18 mA               |

| Supply Voltage                 |                                        |

| REF_OUT and VIO to GND         | -0.3 V to +6.0 V                       |

| VDD to GND                     | -0.3 V to +2.1 V                       |

| VDD to VIO                     | -6 V to +2.4 V                         |

| VS+ to VS-                     | 11 V                                   |

| VS+ to GND                     | -0.3 V to +11 V                        |

| VS- to GND                     | -11 V to +0.3 V                        |

| Digital Inputs to GND          | -0.3 V to VIO +0.3 V                   |

| Digital Outputs to GND         | -0.3 V to VIO +0.3 V                   |

| Temperature                    |                                        |

| Storage Range                  | -65°C to +150°C                        |

| Junction                       | 150°C                                  |

| Lead Soldering                 | 260°C reflow as per JEDEC<br>J-STD-020 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

| Table 7. Thermal Resista |

|--------------------------|

|--------------------------|

| Package<br>Type <sup>1</sup> | θ <sub>JA</sub> | θ <sub>JC_TOP</sub> | θ <sub>JC_BOTTOM</sub> | $\theta_{JB}$ | $\Psi_{JT}$ | $\Psi_{JB}$ | Unit |

|------------------------------|-----------------|---------------------|------------------------|---------------|-------------|-------------|------|

| BC-49-5                      | 53.5            | 54.9                | 58.7                   | 28.8          | 15.6        | 28.6        | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated values are based upon use of a 2S2P JEDEC standard PCB configuration per JEDEC Standard JESD51-7.

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ ESDA/JE-DEC JS-002.

#### ESD Ratings for ADAQ4001

#### Table 8. ADAQ4001, 49-Ball CSP\_BGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 4000                    | 2     |

| FICDM     | 1000                    | C4    |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

\$00

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

003

| A1 BALL<br>CORNER               | 1     | 2        | 3     | 4     | 5     | 6     | 7     |  |

|---------------------------------|-------|----------|-------|-------|-------|-------|-------|--|

| A<br>B<br>C<br>D<br>E<br>F<br>G | 00000 | 00000000 | 00000 | 00000 | 00000 | 00000 | 00000 |  |

Figure 3. Pin Configuration, Top View

|   | 1     | 2     | 3    | 4   | 5       | 6      | 7   |

|---|-------|-------|------|-----|---------|--------|-----|

| A | GND   | VDD   | OUT+ | vs- | REF_OUT | REF    | GND |

| в | R1K-  | R1K-  | OUT+ | VS- | GND     | vio    | VIO |

| с | R1K1- | R1K1- | vs-  | VS- | DNC     | PD_AMP | SDI |

| D | IN-   | IN+   | DNC  | DNC | DNC     | PD_REF | scк |

| E | R1K1+ | R1K1+ | MODE | VS+ | ADCIN+  | GND    | SDO |

| F | R1K+  | R1K+  | OUT- | VS+ | DNC     | DNC    | CNV |

| G | GND   | vсмо  | OUT- | VS+ | VS+     | ADCIN- | GND |

NOTES 1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

Figure 4. Pin Configuration

Table 9. Pin Function Descriptions

| Pin No.                | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                              |

|------------------------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A7, B5, E6, G1, G7 | GND      | Р                 | Power Supply Ground.                                                                                                                                                                                                                                                                                                                                                     |

| A2                     | VDD      | P                 | 1.8 V Power Supply. The VDD range is 1.71 V to 1.89 V.                                                                                                                                                                                                                                                                                                                   |

| A3, B3                 | OUT+     | AO                | Positive Output of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                                                    |

| A4, B4, C3, C4         | VS-      | P                 | Negative Supply of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                                                    |

| A5                     | REF_OUT  | AO                | Reference Buffer Output Voltage.                                                                                                                                                                                                                                                                                                                                         |

| A6                     | REF      | AI                | Reference Buffer Input Voltage.                                                                                                                                                                                                                                                                                                                                          |

| B1, B2                 | R1K-     | AI                | 1 k $\Omega$ Resistor Input to Negative Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                      |

| B6, B7                 | VIO      | Ρ                 | Input and Output Interface Digital Power. Nominally, the VIO pins are at the same supply as the host interface (1.8 V, 2.5 V, 3 V, or 5 V).                                                                                                                                                                                                                              |

| C1, C2                 | R1K1-    | AI                | 1.1 kΩ Resistor Input to Negative Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                            |

| C5, D3 to D5, F5, F6   | DNC      | N/A               | Do Not Connect. Do not connect to this pin.                                                                                                                                                                                                                                                                                                                              |

| C6                     | PD_AMP   | DI                | Power-Down Amplifier. Active low. Connect the PD_AMP pin to GND to power down the fully differential ADC driver. Otherwise, connect the PD_AMP pin to logic high.                                                                                                                                                                                                        |

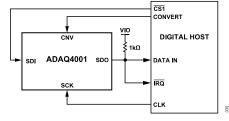

| C7                     | SDI      | DI                | Serial Data Input. This input provides multiple features. SDI selects the interface mode of the ADC as follows:                                                                                                                                                                                                                                                          |

|                        |          |                   | Daisy-chain mode is selected if SDI is low during the CNV rising edge. In this mode, SDI is used as a data input to daisy-chain the conversion results of two or more ADCs onto a single SDO line. The digital data level on SDI is output on SDO with a delay of 16 SCK cycles.                                                                                         |

|                        |          |                   | $\overline{\text{CS}}$ mode is selected if SDI is high during the CNV rising edge. In this mode, either SDI or CNV can enable the serial output signals when low. If SDI or CNV is low when the conversion is complete, the busy indicator feature is enabled. With CNV low, the device can be programmed by clocking in a 16-bit word on SDI on the rising edge of SCK. |

| D1                     | IN-      | AI                | Negative Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                                                     |

| D2                     | IN+      | AI                | Positive Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                                                     |

| D6                     | PD_REF   | DI                | Power-Down Reference Buffer. Active low. Connect the PD_REF pin to GND to power down the reference buffer. Otherwise, connect the PD_REF pin to logic high.                                                                                                                                                                                                              |

| D7                     | SCK      | DI                | Serial Data Clock Input. When the device is selected, the conversion result is shifted out by this clock.                                                                                                                                                                                                                                                                |

| E1, E2                 | R1K1+    | AI                | 1.1 k $\Omega$ Resistor Input to Positive Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                    |

| E3                     | MODE     | DI                | Power Mode for the Fully Differential ADC Driver. Full performance when the MODE pin is high, and low power mode when the MODE pin is low.                                                                                                                                                                                                                               |

| E4, F4, G4, G5         | VS+      | P                 | Fully Differential ADC Driver and Reference Buffer Positive Supply.                                                                                                                                                                                                                                                                                                      |

| E5                     | ADCIN+   | AO                | Positive Input to the ADC. Extra capacitance can be added on the ADCIN+ pin to reduce the RC filter bandwidth.                                                                                                                                                                                                                                                           |

| E7                     | SDO      | DO                | Serial Data Output. The conversion result is output on the SDO pin. SDO synchronizes to SCK.                                                                                                                                                                                                                                                                             |

| F1, F2                 | R1K+     | AI                | 1 k $\Omega$ Resistor Input to Positive Input of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                                      |

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 9. Pin Function Descriptions

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                           |

|---------|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F3, G3  | OUT-     | AO                | Negative Output of the Fully Differential ADC Driver.                                                                                                                                                                                                                                                                 |

| F7      | CNV      | DI                | Convert Input. This input has multiple functions. On its leading edge, CNV initiates the conversions and selects the interface mode of the device: daisy-chain mode or $\overline{CS}$ mode. In $\overline{CS}$ mode, the SDO pin is enabled when CNV is low. In daisy-chain mode, the data is read when CNV is high. |

| G2      | VCMO     | AO                | Fully Differential ADC Driver Output Common-Mode Voltage. Nominally, V <sub>REF</sub> /2.                                                                                                                                                                                                                             |

| G6      | ADCIN-   | AO                | Negative Input to the ADC. Extra capacitance can be added on the ADCIN- pin to reduce the RC filter bandwidth.                                                                                                                                                                                                        |

<sup>1</sup> P is power, AO is analog output, AI is analog input, N/A is not applicable, DI is digital input, and DO is digital output.

VS+ = 5.5 V, VS- = 0 V, VDD = 1.8 V, VIO = 3.3 V,  $V_{REF}$  = 5 V,  $T_A$  = 25°C, high-Z mode disabled, span compression disabled, turbo mode enabled, and  $f_S$  = 2 MSPS, unless otherwise noted.

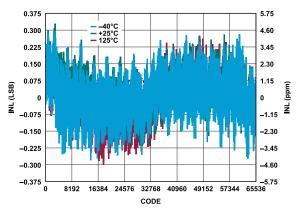

Figure 5. INL vs. Code for Various Temperatures, V<sub>REF</sub> = 5 V, G = 0.454

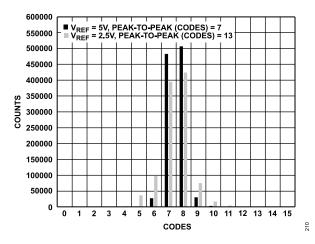

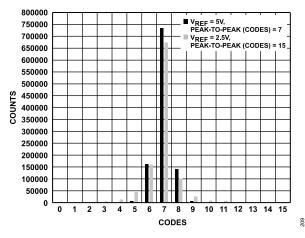

Figure 6. Histogram of a DC Input at the Code Transition,  $V_{REF}$  = 2.5 V and  $V_{REF}$  = 5 V

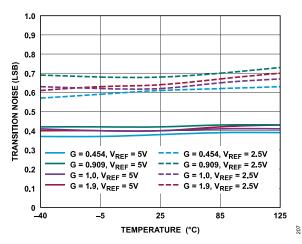

Figure 7. Transition Noise vs. Temperature for G = 0.454, G = 0.909, G = 1, and G = 1.9 and  $V_{REF}$  = 5 V and  $V_{REF}$  = 2.5 V

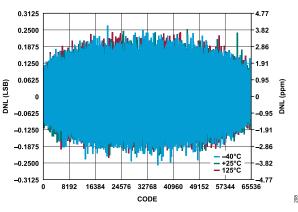

Figure 8. DNL vs. Code for Various Temperatures, V<sub>REF</sub> = 5 V, G = 0.454

Figure 9. Histogram of a DC Input at the Code Center,  $V_{REF}$  = 2.5 V and  $V_{REF}$  = 5 V

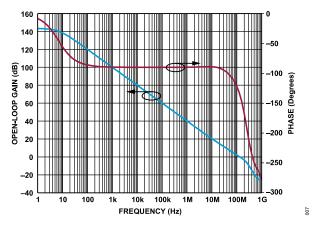

Figure 10. ADC Driver Open-Loop Gain and Phase vs. Frequency

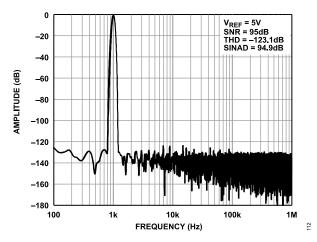

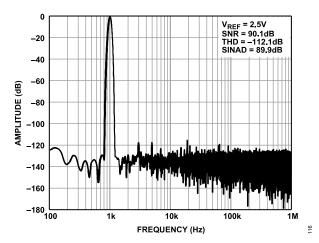

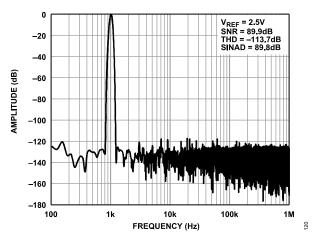

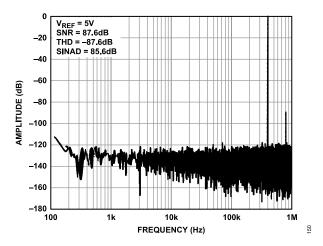

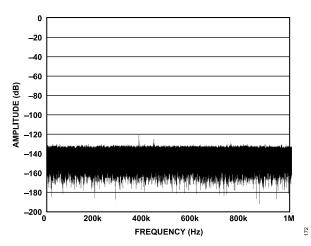

Figure 11. 1 kHz, -0.5 dBFS Input Tone Fast Fourier Transform (FFT), Wide View, G = 1,V<sub>REF</sub> = 5 V, Differential

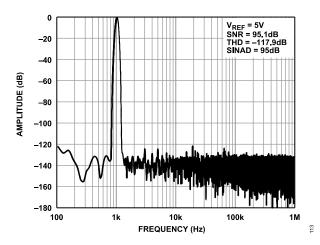

Figure 12. 1 kHz, -0.5 dBFS Input Tone FFT, Wide View, G = 1,  $V_{REF}$  = 5 V, Single-Ended

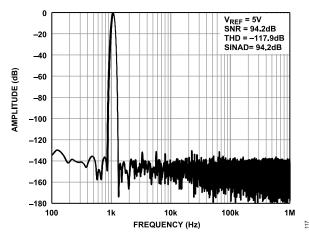

Figure 13. 1 kHz, -0.5 dBFS Input Tone FFT, Wide View, Differential, G = 0.909, V<sub>REF</sub> = 5 V, Low Power Mode

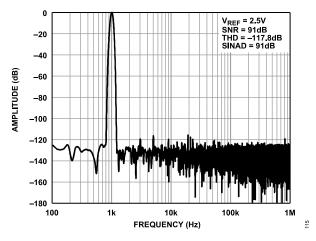

Figure 14. 1 kHz, -0.5 dBFS Input Tone FFT, Wide View, G = 1, V<sub>REF</sub> = 2.5 V, Differential

Figure 15. 1 kHz, -0.5 dBFS Input Tone FFT, Wide View, G = 1, V<sub>REF</sub> = 2.5 V, Single-Ended

Figure 16. 1 kHz, -0.5 dBFS Input Tone FFT, Wide View, Differential, G = 0.909, V<sub>REF</sub> = 2.5 V, Low Power Mode

Figure 17. 100 kHz, -0.5 dBFS Input Tone FFT, Wide View, G = 1, V<sub>REF</sub> = 5 V

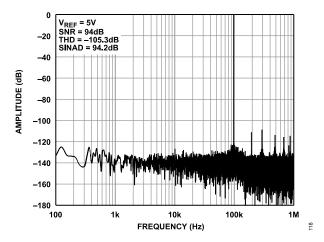

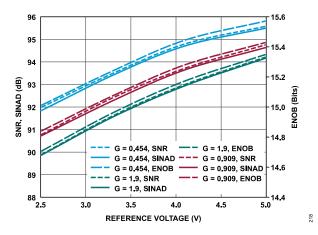

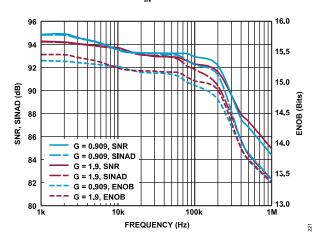

Figure 18. SNR, SINAD, and Effective Number of Bits (ENOB) vs. Reference Voltage for G = 0.454, G = 0.909, and G = 1.9, f<sub>IN</sub> = 1 kHz

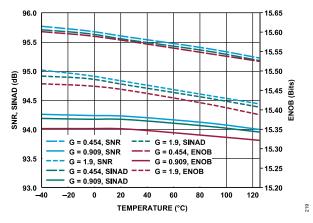

Figure 19. SNR, SINAD, and ENOB vs. Temperature, G = 1.9, G = 0.909, and G = 0.454,  $f_{\rm IN}$  = 1 kHz

Figure 20. 400 kHz, -0.5 dBFS Input Tone FFT, G = 1, Wide View, V<sub>REF</sub> = 5 V

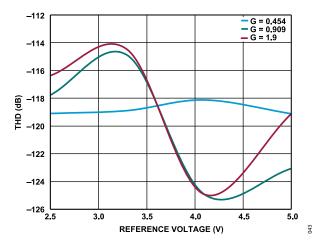

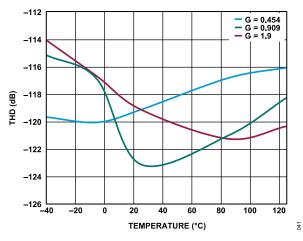

Figure 21. THD vs. Reference Voltage, G = 0.454, G = 0.909, and G = 1.9,  $f_{IN} = 1 \text{ kHz}$

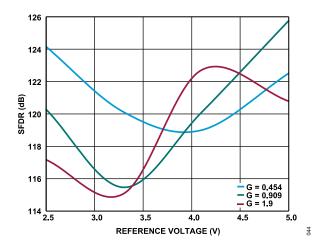

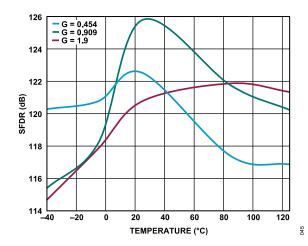

Figure 22. SFDR vs. Reference Voltage for G = 0.454, G = 0.909, and G = 1.9,  $f_{IN} = 1 \text{ kHz}$

Figure 23. THD vs. Temperature for G = 0.454, G = 0.909, and G = 1.9,  $f_{\rm IN}$  = 1 kHz

Figure 24. SNR, SINAD, and ENOB vs. Frequency for G = 1.9 and G = 0.909,  $V_{REF}$  = 5 V

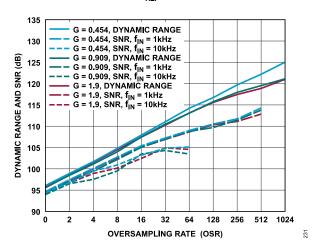

Figure 25. Dynamic Range and SNR vs. Oversampling Rate for G = 0.454, G = 0.909, and G = 1.9, and for Input Frequencies, 2 MSPS

Figure 26. SFDR vs. Temperature for G = 0.454, G = 0.909, and G = 1.9,  $f_{\rm IN}$  = 1kHz

Figure 27. THD and SFDR vs. Frequency for G = 0.909 and G = 1.9, V<sub>REF</sub> = 5 V

Figure 28. Voltage Noise for 0.1 Hz to 10 Hz Bandwidth, 100 kSPS, 250 Samples Averaged per Reading

Figure 29. Operating Current vs. Temperature, 2 MSPS

*Figure 30. Gain Error vs. Temperature, V<sub>REF</sub> = 5.0V, Normal Mode*

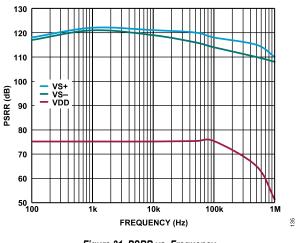

Figure 31. PSRR vs. Frequency

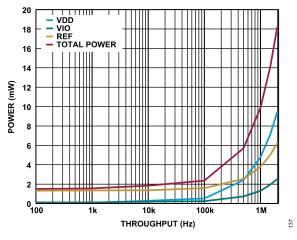

Figure 32. Power vs. Throughput

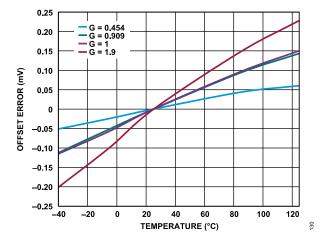

Figure 33. Offset Error vs. Temperature for G = 0.454, G = 0.909, G = 1, and G = 1.9

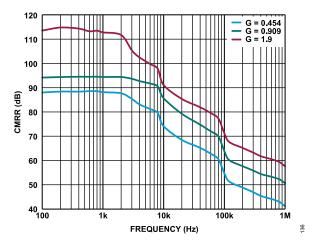

Figure 34. CMRR vs. Frequency for G = 0.454, G = 0.909, and G = 1.9

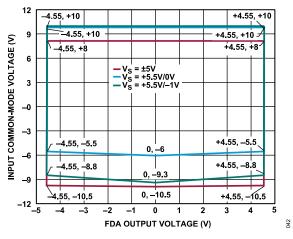

Figure 35. Input Common-Mode Voltage vs. FDA Output Voltage, G = 0.454, Differential Input

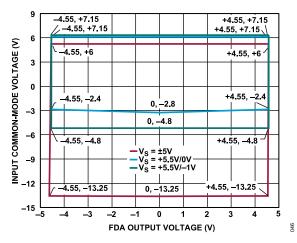

Figure 36. Input Common-Mode Voltage vs. FDA Output Voltage, G = 0.909, Differential Input

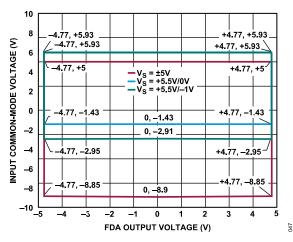

Figure 37. Input Common-Mode Voltage vs. FDA Output Voltage, G = 1.9, Differential Input

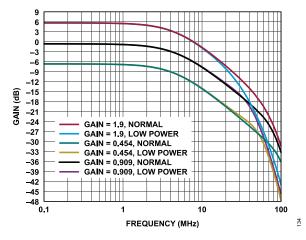

Figure 38. Small Signal Frequency Response for G = 1.9, G = 0.454, and G = 0.909 at Normal and Low Power Mode

Figure 39. Output Drive Recovery, f<sub>IN</sub> = 1 kHz

# TERMINOLOGY

# Integral Nonlinearity (INL) Error

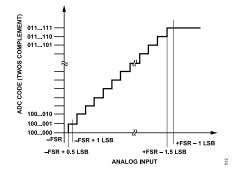

INL error is the deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line (see Figure 40).

# **Differential Nonlinearity (DNL) Error**

In an ideal ADC, code transitions are 1 LSB apart. DNL is the maximum deviation from this ideal value. DNL error is often specified in terms of resolution for which no missing codes are guaranteed.

### **Offset Error**

The first transition occurs at a level  $\frac{1}{2}$  LSB above analog ground. Offset error is the difference between the ideal midscale input voltage (0 V) and the actual voltage producing the midscale output code.

#### **Offset Error Drift**

Offset error drift is the ratio of the offset error change due to a temperature change of 1°C and the full-scale code range. Offset error drift is expressed in parts per million per degree Celsius as follows:

Offset Error Drift (ppm/°C) =  $10^6 \times (Offset Error_T_{MAX} - Offset Error_T_{MIN} / (T_{MAX} - T_{MIN})$

where:

$T_{MAX} = 125 \text{ °C.}$  $T_{MIN} = -40 \text{ °C}$ .

#### Gain Error

The first transition occurs at a level  $\frac{1}{2}$  LSB above nominal negative full scale and the last transition occurs for an analog voltage  $\frac{1}{2}$  LSB below the nominal full scale. The gain error is the deviation of the difference between the actual level of the last transition and the actual level of the first transition from the ideal levels after the offset error is removed. Gain error is expressed as a percentage as follows:

Gain Error (%) =

$$100 \times ((PFS - NFS)_{ACTUAL\_CODE} - (PFS - NFS)_{IDEAL\_CODE}) / (PFS - NFS)_{IDEAL\_CODE}$$

(2)

where:

*PFS* is the positive full scale. *NFS* is the negative full scale.

# **Gain Error Drift**

Gain error drift is the ratio of the gain error change due to a temperature change of 1°C and the full-scale range. Gain error drift is expressed in parts per million per degree Celsius as follows:

Gain Error Drift (ppm/°C) =  $10^6 \times$  (Gain Error\_ $T_{MAX}$  – Gain Error\_ $T_{MIN}$ ) / ( $T_{MAX}$  –  $T_{MIN}$ ) (3)

where:

$T_{MAX} = 125$  °C.  $T_{MIN} = -40$  °C.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in decibels (dB), between the rms amplitude of the input signal and the peak spurious signal, including harmonics.

#### Effective Number of Bits (ENOB)

ENOB is a measurement of the resolution with a sine wave input. ENOB is related to SINAD as follows:

$ENOB = (SINAD_{dB} - 1.76)/6.02$

(4)

ENOB is expressed in bits.

### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first five harmonic components to the rms value of a full-scale input signal and is expressed in decibels.

### **Dynamic Range**

(1)

Dynamic range is the ratio of the rms value of the full scale to the total rms noise measured. The value for dynamic range is expressed in decibels. Dynamic range is measured with a signal at -60 dBFS so that the range includes all noise sources and DNL artifacts.

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

#### Signal-to-Noise-and-Distortion Ratio (SINAD)

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components that are less than the Nyquist frequency, including harmonics but excluding dc. The value of SINAD is expressed in decibels.

#### **Aperture Delay**

Aperture delay is the measure of the acquisition performance and is the time between the rising edge of the CNV input and when the input signal is held for a conversion.

# TERMINOLOGY

### **Transient Response**

Transient response is the time required for the ADC to acquire a full-scale input step to  $\pm 1$  LSB accuracy.

# Common-Mode Rejection Ratio (CMRR)

CMRR is the ratio of the power in the  $\mu$ Module output at the frequency, f, to the power of a 1.3 V p-p sine wave applied to the input common-mode voltage of f.

(5)

CMRR (dB) = 10log( $P_{\mu Module_{IN}}/P_{\mu Module_{OUT}}$ )

where:

$P_{\mu Module\_IN}$  is the common-mode power at f applied to the inputs.  $P_{\mu Module\_OUT}$  is the power at f in the  $\mu$ Module output.

### Power Supply Rejection Ratio (PSRR)

PSRR is the ratio of the power in the  $\mu$ Module output at f to the power of a 500 mV p-p sine wave applied to the VDD and VS+ supply voltage centered at 5 V and 100 mV p-p for a VS- supply voltage centered at – 1 V of f.

PSRR (dB) = 10log( $P_{\mu Module\_IN}/P_{\mu Module\_OUT}$ )

where:

$P_{\mu Module_{IN}}$  is the power at f at each of the VDD, VS+, and VS-supply pins.

$P_{\mu Module OUT}$  is the power at f in the  $\mu$ Module output.

### THEORY OF OPERATION

#### **CIRCUIT INFORMATION**

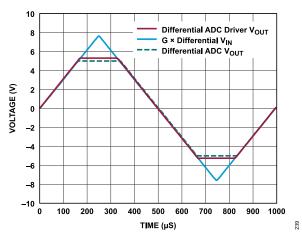

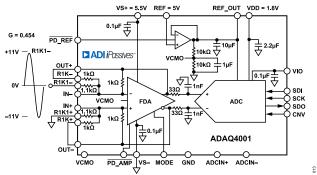

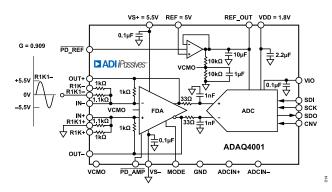

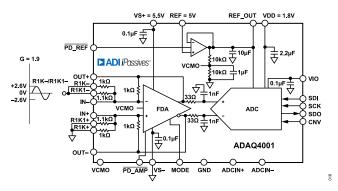

The ADAQ4001 SiP is a fast, precision DAQ signal chain that uses SAR architecture. As shown in Figure 1, the ADAQ4001  $\mu$ Module DAQ solution contains a high bandwidth, fully differential ADC driver, a low noise reference buffer, and a 16-bit SAR ADC, along with the critical precision passive components required to achieve optimized performance with pin-selectable gain options of 0.454, 0.909, 1, or 1.9. All active components in the circuit, including *i*Passives thin film resistors with ±0.005% matching, are designed by Analog Devices and are factory calibrated to achieve a high degree of specified accuracy and minimize temperature dependent error sources.

The ADAQ4001 is capable of converting 2,000,000 samples per second (2 MSPS). The ADAQ4001 has a valid first conversion after being powered down for long periods that can reduce power consumed in applications where the ADC does not convert constantly.

The ADAQ4001 offers a significant reduction in form factor and total cost of ownership compared to traditional discrete signal chains from a selection of individual components, PCB size, and manufacturing perspective, while still providing the flexibility to adapt to a wide array of applications.

The ADAQ4001 incorporates a fully differential, high speed ADC driver with integrated precision resistors. The precision resistors can be pin strapped to achieve different gains for the fully differential ADC driver, which allows the user to match the input signal range. The fully differential ADC driver can be used in a differential manner or to perform a single-ended to differential conversion for a single-ended input.

The fast conversion time of the ADAQ4001, along with turbo mode, allows low clock rates to read back conversions, even when the ADAQ4001 is running at its maximum throughput rate. Note that for the ADAQ4001, the full throughput rate of 2 MSPS can be achieved only with turbo mode enabled. Because the ADAQ4001 has on-board conversion clocks, the serial clock (SCK) is not required for the conversion process.

The ADAQ4001 interfaces to any 1.8 V to 5 V digital logic family. The device is housed in a 7 mm × 7 mm, 0.80 mm pitch, 49-ball CSP\_BGA that provides significant space savings and allows flexible configurations.

#### TRANSFER FUNCTIONS

The ideal transfer characteristics for the ADAQ4001 are shown in Figure 40 and Table 10.

Figure 40. ADC Ideal Transfer Function (FSR Is Full-Scale Range)

|                  |                                            | Analog Inputs                                              |                     |  |  |  |

|------------------|--------------------------------------------|------------------------------------------------------------|---------------------|--|--|--|